BÁO cáo THIẾT kế VI MẠCH số

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (2.56 MB, 28 trang )

ĐẠI HỌC QUỐC GIA THÀNH PHỐ HỒ CHÍ MINH

TRƯỜNG ĐẠI HỌC BÁCH KHOA

KHOA ĐIỆN-ĐIỆN TỬ

NĂM HỌC 2019 – 2020

-------*-------

BÁO CÁO

THIẾT KẾ VI MẠCH SỐ

GVHD: Trần Hoàng Linh

Trợ giảng:Dương Quang Hổ

SVTH:Phùng Tuấn Hưng

MSSV:1611444

TP. HỒ CHÍ MINH, THÁNG 11 NĂM 2019

download by :

Mục lục

BÀI 1: THIẾT KẾ VÀ ĐO ĐẠC CỔNG NOT .............................................................................. 3

1.

Thiết kế sơ đồ nguyên lý ...................................................................................................... 3

2.

Thực hiện mô phỏng đáp ứng DC........................................................................................ 4

3.

Thực hiện mô phỏng transient ............................................................................................. 5

4.

Layout cổng NOT ................................................................................................................ 7

BÀI 2: THIẾT KẾ VÀ ĐO ĐẠC CỔNG NAND-NOR ................................................................. 8

1.

Thiết kế sơ đồ nguyên lý cổng NAND ................................................................................ 8

2.

Mô phỏng đáp ứng DC cổng NAND ................................................................................... 9

3.

Mô phỏng đáp ứng Transient cho cổng NAND ................................................................. 11

4.

Thiết kế layout cổng NAND .............................................................................................. 12

5.

Cổng NOR ......................................................................................................................... 13

6.

Mô phỏng DC cổng NOR: ................................................................................................. 13

7.

Mô phỏng transient cổng NOR .......................................................................................... 15

8.

Thiết kế layout cổng NOR ................................................................................................. 16

Bài 3: Thực hiện cổng FLIP-FLOP và CHARACTERIZATION ................................................ 17

1.

Thiết kế sơ đồ nguyên lý .................................................................................................... 17

2.

Kiểm tra đáp ứng TRANSIENT ........................................................................................ 18

Bài 4: SRAM................................................................................................................................. 20

1.

SRAM ở chế độ write ........................................................................................................ 20

2.

Sram ở read ........................................................................................................................ 22

Bài 5: TCAM ................................................................................................................................ 25

1.

TCAM ở chế độ write ........................................................................................................ 25

2.

TCAM ở chế độ operation ................................................................................................. 27

2

download by :

BÀI 1: THIẾT KẾ VÀ ĐO ĐẠC CỔNG NOT

1. Thiết kế sơ đồ nguyên lý

A

1

0

Y

0

1

Bảng 3-1: Bảng sự thật cổng NOT

Sơ đồ nguyên lý và ký hiệu cổng:

Hình 1-1: Sơ đồ cổng NOT

Hình 1-2: Ký hiệu cổng NOT

3

download by :

2. Thực hiện mô phỏng đáp ứng DC

Thông số:

Thông số

Vdd

Cload

Vin

Giá trị

1V

1f F

0-1 V

Sơ đồ nguyên lý:

Điện áp ngõ ra tại các Vin:

Vin 0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

Vout 1 0.9998 0.9977 0.9855 0.9461 0.7627 0.1322 0.0378 0.007

0.9

1

0.0007 0.00006

4

download by :

Dạng sóng ngõ ra:

3. Thực hiện mơ phỏng transient

Thơng số mạch:

Thông số

Vdd

Cload

Voltage 1

Voltage 2

Rise time

Fall time

Delay

Pulse width

Period

Giá trị

1V

1f F

0V

1V

1p s

1p s

0n s

1n s

2n s

5

download by :

Mạch nguyên lý:

Kết quả mô phỏng:

6

download by :

Thông số

Trise – Rising Time (20% - 80%)

Tfall – Falling Time (80% - 20%)

Trise – Rising Time (10% - 90%)

Tfall – Falling Time (90% - 10%)

Trise_propagation delay (90% - 50%)

Tfall_propagation delay (10% - 50%)

Tpropagation delay (50% - 50%)

Dynamic Power

Switching Power

Kết quả

3.253E-12 s

3.253E-12 s

4.768E-12 s

4.768E-12 s

4.184E-12 s

4.184E-12 s

1.282E-12 s

2.5n W

4. Layout cổng NOT

7

download by :

BÀI 2: THIẾT KẾ VÀ ĐO ĐẠC CỔNG NAND-NOR

1. Thiết kế sơ đồ nguyên lý cổng NAND

A

0

X

1

B

X

0

1

Y

1

1

0

Bảng sự thật cồng NAND

Sơ đồ nguyên lý:

Ký hiệu cổng:

8

download by :

2. Mô phỏng đáp ứng DC cổng NAND

Thông số mạch:

Sơ đồ nguyên lý:

9

download by :

Kết qủa mô phỏng:

Điện áp ngõ ra tại các Vin:

Vin

Vout

0.1

0.999

0.2

0.998

0.3

0.987

0.4

0.753

0.5

0.036

0.6

0.004

0.7

0.0004

0.8

0.00004

0.9

0.00002

1

0.00001

10

download by :

3. Mô phỏng đáp ứng Transient cho cổng NAND

Sơ đồ nguyên lý:

Kết quả mô phỏng:

11

download by :

4. Thiết kế layout cổng NAND

Sơ đồ stick digram:

Layout:

12

download by :

5. Cổng NOR

Sơ đồ nguyên lý:

6. Mô phỏng DC cổng NOR

Sơ đồ:

13

download by :

Kết quả mô phỏng:

Điện áp ngõ ra tại các Vin:

Vin

Vout

0.1

0.998

0.2

0.979

0.3

0.857

0.4

0.091

0.5

0.021

0.6

0.007

0.7

0.001

0.8

0.0001

0.9

1

0.00001 0.000001

14

download by :

7. Mô phỏng transient cổng NOR

Sơ đồ:

Kết quả mô phỏng:

15

download by :

8. Thiết kế layout cổng NOR

Sơ đồ stick digram:

Layout:

16

download by :

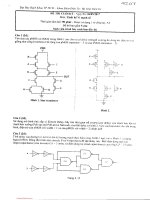

Bài 3: Thực hiện cổng FLIP-FLOP và

CHARACTERIZATION

1. Thiết kế sơ đồ nguyên lý

Bảng sự thật cổng DFF

Sơ đồ nguyên lý cổng:

17

download by :

2. Kiểm tra đáp ứng TRANSIENT

Mạch mô phỏng:

18

download by :

Kết quả mô phỏng:

19

download by :

Bài 4: SRAM

1. SRAM ở chế độ write

Sơ đồ mô phỏng:

Nguyên lý mô phỏng:chế độ write là chế độ dữ liệu được ghi vào SRAM tại các nút ghi_BL và

ghi_BLX,2 nút này luôn trái ngược điện áp và giống dữ liệu đầu vào tương ứng là BL và BLX.

Quá trình ghi chỉ thực hiện khi WL=1.

20

download by :

Kết quả mô phỏng sram writing:

21

download by :

2. Sram ở read

Sơ đồ mô phỏng:

Nguyên lý mô phỏng:dữ liệu của SRAM đã được lưu tại các nút noi_BL và noi_BLX,2 dữ liệu

này luôn ngược dấu nhau. Khi WL=1 bắt đầu chế độ read dữ liệu điện tại các nút lưu trữ sẽ được

hiển thị tương ứng tại các dây BL,BLX.

22

download by :

Kết quả mô phỏng sram read:

23

download by :

24

download by :

Bài 5: TCAM

1. TCAM ở chế độ write

Sơ đồ nguyên lý:

Chế độ hoạt động như SRAM

25

download by :