BÁO cáo 1 THÍ NGHIỆM THIẾT kế VI MẠCH số

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (638.29 KB, 26 trang )

ĐẠI HỌC QUỐC GIA

ĐẠI HỌC BÁCH KHOA TP HỒ CHÍ MINH

BÁO CÁO THÍ NGHIỆM THIẾT KẾ VI MẠCH SỐ

1.1 THIẾT KẾ SƠ ĐỒ NGUYÊN LÝ

Bảng 3-1 Bảng sự thật của cổng NOT

A

0

1

Y

1

0

Sơ đồ nguyên lý & ký hiệu cổng:

Hình 1-1 Sơ đồ nguyên lý cổng NOT

Hình 1-2 Ký hiệu cổng NOT

1.2 THỰC HIỆN MƠ PHỎNG ĐÁP ỨNG DC

Sử dụng ADEL để thực hiện mô phỏng đáp ứng DC của cổng NOT, thực hiên cấp tín hiệu input dạng

xung RAMP tầm điện áp thay đổi từ 0 đến 1V và khảo sát đáp ứng ngõ ra.

Thông số

VDD

Cload

Vin

Giá trị

1V

1f F

0 V – 1V

Sơ đồ mạch đo DC:

Thực hiện đo điện áp ngõ ra tại các giá trị Vin sau:

Vin

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

Vout

0.9995

0.9948

0.9655

0.8463

0.1605

0.0472

0.0153

0.0029

308.7E-6

24.8E-6

Thực hiện vẽ lại dạng sóng Vout:

Nhận xét: Theo lý thuyết, Vin=0 -> Vout=1, Vin=1 -> Vout=0, điểm chuyển áp lý tưởng V M=1/2=0.5. Theo

số liệu đo đạc thực tế, ta nhận thấy một chút sai số nhỏ do dòng rị và sai số linh kiện. Tuy vậy, ta có thể kết

luận mạch khảo sát đúng theo nguyên lý hoạt động của cổng NOT .

1.3 THỰC HIÊN MÔ PHỎNG ĐÁP ỨNG TRANSIENT

Thông số mạch:

Thông số

VDD

Cload

Voltage 1

Voltage 2

Rise time

Fall time

Delay

Pulse width

Period

Giá trị

1V

1 fF

0V

1V

1 ps

1 ps

0 ns

1 ns

2 ns

Mạch kiểm tra hoạt động của cổng NOT:

Kết quả mô phỏng:

Thực hiện đo những giá trị sau của đáp ứng ngõ ra:

Thông số

Kết quả

Trise – Rising Time (20% - 80%)

15.8 ps

Tfall – Falling Time (80% - 20%)

9.5 ps

Trise – Rising Time (10% - 90%)

22.5 ps

Tfall – Falling Time (90% - 10%)

13.8 ps

Dynamic Power

709.4 nW

Switching Power

1.4 THỰC HIÊN VẼ LAYOUT CHO CỔNG NOT

Hoàn thành stick diagram:

Hoàn thành layout của cổng NOT:

2.1 THIẾT KẾ SƠ ĐỒ NGUYÊN LÝ CỔNG NAND2

Bảng 2-1 Bảng sự thật của cổng NAND2

A

0

X

1

B

X

0

1

Y

1

1

0

Bảng 2-2 Bảng giá trị kích thước của NMOS và PMOS

WN

LN

WP

LP

Sơ đồ nguyên lý & Ký hiệu cổng

90n

50n

90n

50n

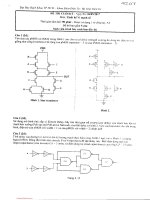

Hình 2-3 Sơ đồ nguyên lý cổng NAND2

Hình 2-4 Ký hiệu cổng NAND2

2.2 MÔ PHỎNG ĐÁP DC CỔNG NAND2

Sử dụng ADEL để thực hiện mô phỏng đáp ứng DC của cổng NAND2, thực hiên cấp tín hiệu input

dạng xung RAMP tầm điện áp thay đổi từ 0 đến 1V và khảo sát đáp ứng ngõ ra.

Thông số

Vin1

Vin2

Sơ đồ mạch đo DC:

Giá trị

1V

1 fF

0 V – 1V

0 – 1V

Thực hiện đo điện áp ngõ ra tại các giá trị Vin sau:

Vin1

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

Vin2

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

Vout

1

0.999

0.996

0.979

0.919

0.264

0.060

0.011

0.001

0.0001

Thực hiện vẽ lại dạng sóng Vout

Nhận xét: Khoảng chuyển tiếp từ 1 xuống 0 của mạch kéo dài, hơi lệch phải so với mốc 0.5V. Khi mạch

nhận tín hiệu điện áp mức thấp mạch kéo lên chỉ đi qua 1 PMOS, khoảng điện áp cho phép kéo dài, khi nhận

tín hiệu điện áp mức cao, phải dẫn qua 2 NMOS nên điện áp cho phép cần phải cao ( >0,6).

2.3 MÔ PHỎNG ĐÁP ỨNG TRANSIENT CỔNG NAND2

Sử dụng ADE L để kiểm tra hoạt động của cổng NAND2 với các thiết lập cho mạch testbench như sau:

Vdd= 1 V, Cload = 1f , Vpulse cho ngõ vào A (voltage 1 = 0 V, voltage 2 =

1 V, delay = 0 ns, rise time = fall time = 1 ps, pulse width = 1 ns, period = 2 ns), Vpulse cho ngõ vào

B (voltage 1 = 0 V, voltage 2 = 1 V, delay = 0 ns, rise time = fall time = 1 ps, pulse width = 2.5 ns,

period = 5 ns) và thời gian mô phỏng transient là 8 ns. Mạch Testbench:

Hình 2-5 Mạch kiểm tra hoạt động của cổng NAND2

Kết quả mơ phỏng:

2.4 THIẾT KẾ LAYOUT CỔNG NAND2

- Hồn thành stick diagram cổng NAND2:

- Hoàn thành layout của cổng NAND2

2.5 THIẾT KẾ SƠ ĐỒ NGUYÊN LÝ CỔNG NOR2

Bảng 2-3 Bảng sự thật của cổng NOR2

A

0

0

1

B

0

X

X

OUT

1

0

0

Bảng 2-4 Bảng giá trị kích thước của NMOS và PMOS

WN

LN

WP

LP

Sơ đồ nguyên lý & Ký hiệu cổng

90n

50n

90n

50n

Hình 2-6 Sơ đồ nguyên lý cổng NOR2

Hình 2-7 Ký hiệu cổng NOR2

2.6 MƠ PHỎNG ĐÁP DC CỔNG NOR2

Sử dụng ADEL để thực hiện mô phỏng đáp ứng DC của cổng NAND2, thực hiên cấp tín hiệu input

dạng xung RAMP tầm điện áp thay đổi từ 0 đến 1V và khảo sát đáp ứng ngõ ra.

Thông số

VDD

Cload

Vin1

Vin2

Giá trị

1V

1 fF

0V – 1V

0V – 1V

Thực hiện đo điện áp ngõ ra tại các giá trị Vin sau:

Vin1

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

Vin2

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

Vout

0.998

0.979

0.858

0.092

0.021

0.007

0.001

0.165

0.014 0.001

Sơ đồ mạch đo DC:

Thực hiện vẽ lại dạng sóng Vout :

Nhận xét: Khoảng chuyển tiếp từ 1 xuống 0 của mạch kéo dài, lệch trái so với mốc 0.5V. Do khi mạch nhận

tín hiệu điện áp mức thấp mạch kéo lên phải đi qua 1 PMOS, khi nhận tín hiệu điện áp mức cao, mạch chỉ

dẫn qua 1 NMOS nên điện áp cho phép khơng cần cao (< 0.4).

2.7 MƠ PHỎNG ĐÁP ỨNG TRANSIENT CỔNG NOR2

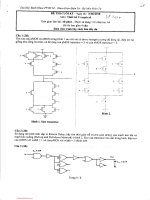

Hình 2-8 Mạch kiểm tra hoạt động của cổng NOR2

Kết quả mô phỏng:

2.4 THIẾT KẾ LAYOUT CỔNG NOR2

- Hoàn thành stick diagram cổng NOR2:

- Hoàn thành layout của cổng NOR2:

3.1 THIẾT KẾ SƠ ĐỒ NGUYÊN LÝ DFF

Bảng 3-1 Bảng sự thật của cổng DFFNEG

CLK

0, 1,

0, 1,

D

X

X

0

1

Q

0

1

X

X

Bảng 3-22 Bảng giá trị kích thước của NMOS và PMOS

WN

LN

WP

LP

90n

50n

90n

50n

Sơ đồ nguyên lý & Ký hiệu cổng:

Hình 3-3 Sơ đồ nguyên lý cổng DFFNEG

Qnext

0

1

0

1

Hình 3-4 Ký hiệu cổng DFFNEG

3.2 KIỂM TRA ĐÁP ỨNG TRANSIENT

Sử dụng ADE L để kiểm tra hoạt động của cổng DFFNEG với các thiết lập cho mạch testbench như sau:

Vdd= 1 V, Cload = 1 f , Vpulse cho ngõ vào D (voltage 1 = 0 V, voltage 2 =

1V, delay = 0 ns, rise time = fall time = 1 ps, pulse width = 2 ns, period = 4 ns), Vpulse cho ngõ vào

CLK (voltage 1 = 0 V, voltage 2 = 1 V, delay = 0 ns, rise time = fall time = 1 ps, pulse width = 1 ns,

period = 2 ns) và thời gian mô phỏng transient là 20 ns. Mạch testbench và kết quả dạng sóng thu

được như hình dưới đây:

Hình 3-5 Mạch kiểm tra hoạt động của cổng DFFNEG