Gigabyte b560 hd3 rev1 0

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (2.2 MB, 70 trang )

5

4

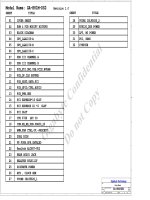

Model Name: B560 HD3

D

C

D

l

a

i

t

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

REALTEK 8118 LAN

Realtek ALC897

REAR AUDIO JACK

CPU POWER-1

CPU POWER-1

F_PANEL, NCT3933

IT5702

PCH/AUDIO/DEBUG/C_LED1/2

D_LED1/D_LED2

SMBUS SWITCH

EMI-ESD

POWER MAP

NTC MAP

DL_DQ1 DK_DQ1 DJ_DQ1 DI_DQ1

DH_DQ1 DG_DQ1 DF_DQ1

VCORE

CHOKE

DK

DJ

DI

DH

DG

DF

12

11

10

9

8

7

6

CHOKE

B

DB_DQ1

VCORE

DX_DQ1

VCCGT

1

DX_DL1

DA_DQ1

1

DA

PCH

DC_DQ1

2

DB

DANTC1

DD_DQ1

3

DC

CPU SOCKET

DrMOS

DE_DQ1

DL

DBNTC1

A

HDMI, DP

DP_VGA SWITCH

REAR USB 30

Gigabyte Technology

Title

Size

Custom

Date:

5

C

VRM_TEMP

DrMOS

4

VCORE_PSTAGE-1_L=0.15u

VCORE_PSTAGE-2_L=0.15u

POSCAP_0+0_H510-B560

VCCGT_PSTAGE_L=0.15u

VCCSA_MOS

VCCIO-Ferrite-Z系系

VCCIO2-Ferrite-Z系系

RT8237_DDR_B560

RT8120_VPP_CHOKE-合合

NCP81269_VCC18_PCH

RT8068_VCC1V8_PRIM

DISCRETE POWER

ATX POWER , A_-PROCHOT

DVI

DD

M.2 x4 (P)

COM,LPT,TPM, THB

ISL69269_L=0.15u

rev 1.0

1

TITLE

GL850S_ F_USB20 X4

KB_MS, F_USB30

5

A

TITLE

COVER SHEET

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

CPU_LGA1200-A

CPU_LGA1200-B-DDR4

CPU_LGA1200-C

CPU_LGA1200-D

DDR 4 CHANNEL A

DDR 4 CHANNEL B

PCH CLK,DMI,CNVI

PCH SPI,USB

PCH PCIE,SATA

PCH ESPI,MISC

PCH GPP,HDA

PCH PWR, GND

Heatsink

ITE ITE8689

HWM

FAN CTRL-CFL-SIO_5 FAN

Single BIOS for CS mode

PCI EXPRESS X16 SLOT

PCI EXPRESS X4 SLOT(PCH)

PCI EXPRESS X1 *2

RT2168 DP TO VGA

M.2 x4 (A)

2

SHEET

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

DE

B

SHEET

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

3

4

3

2

Cover Sheet

Document Number

Rev

B560 HD3 Sheet

Tuesday, January 26, 2021

1

1.0

1

of

70

8

7

6

5

Model Name: B560 HD3

rev1.0

4

3

2

Circuit or PCB layout change

DATE

Change Item

1

Reason

D

D

Component value change history

Data

Change Item

2020/07/09

Update AUDIO & LED 模模

2020/07/14

Update SIO 模模, ADD OR16~20

2020/08/13

Update Audio ALC1200 to ALC1220

Update PCH 模模(R011_200812)

2020/08/18

Update PCH POWER模模模模模模

DGR6 不不不, DGQ14 & DGR5 不不

Update CPU POWER 模模模模模模

NPA_R14模改2.8K/4/1, NPA_R16 模改1.8K/4/1

C

2020/09/02

intel 500 note rev 0.3

2020.12.23

1.0 BOM Release

PCB: 1.0

2021.01.13

1.0 BOM Release

PCB: 1.0

2021.01.27

1.0 BOM Release

PCB: 1.0

2020/09/02

l

a

i

t

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

Reason

C

電電 10u 0603 16V 全全模改10u 0805 16V(FAN & LED)

B

1. COUPON2 5VDUAL --> GND (P.44)

2. PWM ADD LCOATION : DAR162 (P.30)

3. DP (P.47)

4. DP SWITCH (P.48)

5. USB20 N_+USBP/N2 (P.11)

6. LAN ESD 5VDUAL -->3VDUAL_LAN1

7. WR104 VCCST_VCCPLL--> VCCSTG

8. SMBUS SWITCH BOM CHECK !!

1. PWM 00R-->24R

2. IT5702 20R主主 A1R 替主

3. BOM: 9MB56HD3-00-10A-->9MB56HD3-00-10B

4. U4 REMOVE

1. location : OR27 remove

2. BOM: 9MB56HD3-00-10B-->9MB56HD3-00-10C

B

A

A

Title

BOM & PCB MODIFY HISTORY

Size

Document Number

Custom

Date:

8

7

6

5

4

3

Rev

B560 HD3

Wednesday, January 27, 2021

2

1.0

Sheet

2

1

of

70

8

7

6

5

4

3

2

1

REV:0.1

CHOKE與CAP主料料料

VCC1V8_PRIM

VCC1V8_PRIM

D

3VDUAL

NPB_R1

8.2K/4/X

NPB_R2

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

VIN_VCC1V8P

0/6/SHT/30/M/X

NPB_C3

1

NPB_C9

NPB_ZD1

AZ2225-01L/SOD323

10u/6/X5R/6.3V/M

10u/6/X5R/6.3V/M

NPB_C4

1u/6/X7R/16V/K

C

l

a

ti

VCC1V8P_EN

9

10

PVIN

PVIN

8

SVIN

5

VCC1V8_PRIM

PGOOD

EN

LX

1

LX

2

LX

3

FB

6

NC

7

VCC1V8P_PHASE

NPB_R3

2K/4/1

VCC1V8P_ADJ

<63> VCC1V8P_ADJ

GND

11

NPB_R4

1K/4/1

ADDRESS=2A

VREF=03

NPB_C1

22u/6/X5R/6.3V/M/X

VOUT = 1.8V

ICCMAX = 2.07A

NPB_L1

1.0uH/15A/S/6.7m

NPB_U1

4

<41> VCC1V8P_GD

5VSB

D

L=1u

DCR=7.4 mohm

Isat=15A

Idc=12A

請請請CHOKE一一一一請.先先先.

請請請請請ripple後後後後後後不不

NPB_C2

22p/4/NPO/50V/J

C

RT8068AZQW/WDFN-10L

NPB_C10

1u/4/X5R/6.3V/K/X

B

PWR SEQ

VCC1V8_PRIM CAP

5VDUALcheck power

NPB_R5

8.2K/4/X

B

22u*4PCS

VCC1V8_PRIM

不不

VCC1V8P_EN

NPB_C5

22u/6/X5R/6.3V/M

NPB_C6

22u/6/X5R/6.3V/M

NPB_C7

22u/6/X5R/6.3V/M

NPB_C8

22u/6/X5R/6.3V/M

connect to PCH pin AD46

<11,41> SLP_SUS_N

NPB_R6

VCC1V8P_EN

0/4

A

A

Title

RT8068_VCC1V8_PRIM

Size

Document Number

Custom

Rev

1.0

B560 HD3

Date:

8

7

6

5

4

3

Tuesday, January 26, 2021

2

Sheet

2

of

1

70

5

4

3

2

BLOCK DIAGRAM

PCI EXPRESS X16

D

DP

VGA

CHANNEL A

DDR4 DIMM X 2

PCIE-16 gen3

HDMI

DDI3

DVI

DDI2

SWITCH

REALTEK 8118 LAN

DDR4 BUS

INTEL LGA1200

DDI1

l

a

i

t

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

PCIE-4 gen4

PCIE-1 gen3

FDI

Rear - 4 USB 3.0,

2 USB 2.0

C

Front - 2 USB 3.0,

6 USB 2.0

GL850 USB2.0 HUB

GL850 USB2.0 HUB

1

CHANNEL B

DDR4 DIMM X 2

D

M2P

DMI

USB 2.0/3.0

USB 2.0/3.0

USB 2.0

USB 2.0

PCI EXPRESSX4

PCIE-1 gen3

PCI EXPRESSX1_1/1_2

PCIE-1 gen3

B

PCH

(B560)

C

SATA / PCIE

SATAIII X6

SATA III / II

M.2A SLOT

SPI BUS

LPC BUS

SPI SINGLE BIOS(256M)

LPC I/O ITE8689

B

AZALIA BUS

I/O PORTS :

COM

KB/PS2

Realtek ALC897

AUDIO PORTS :

LIN_ OUT

LINE_IN

SURR BACK

CEN/LFE

FRONT AUDIO

MIC

SURR

FRONT PANEL /

CPU/SYS FAN

COM / LPT

A

A

Gigabyte Technology

Title

BLOCK DIAGRAM

Size

C

Date:

5

4

3

2

Document Number

Rev

B560 HD3 Sheet

Tuesday, January 26, 2021

1

1.0

3

of

70

5

4

SKT_H4

LGA1200E

<10> N_CPUCLK

<10> N_-CPUCLK

<10> N_CPUPCIBCLK

<10> N_-CPUPCIBCLK

VCCST_VCCPLL

<10> N_24MCLK

<10> N_-24MCLK

WR4

56.2/4/1

D

<30>

<30>

<30>

<17,30>

-PVIDALRT

PVIDSLCK

PVIDSOUT

A_-PROCHOT

LGA1151

N_CPUCLK

N_-CPUCLK

U1

T1

N_CPUPCIBCLK

N_-CPUPCIBCLK

T4

T3

PCI_BCLKP

PCI_BCLKN

N_24MCLK

N_-24MCLK

U8

U7

CLK24P

CLK24N

BCLKP

BCLKN

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

WR2

100/4/1

WR5

WR7

WR1

WR81

A_-PVIDALRT_R

220/4/1

0/4/SHT/M/X A_PVIDSLCK_R

0/4/SHT/M/X A_PVIDSOUT_R

A_-PHOT

499/4/1

A14

C14

B14

A16

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

AC33

AC37

B13

<39> DDR_VTT_CTL

<14> A_-SKTOCC

<12,17> N_PCH_VRMPWRGD

VCCST_VCCPLL

DDR_VTT_CNTL

SKTOCC#

VCCST_PW RGD

WR34

6.04K/4/1

WR3

2.8K/4/1

WR70

1K/4/1

<10,68> N_CPUPWROK

<12> N_-CPURST

<12> A_PMSYNC

<12> A_PMDOWN

<12,17> A_PECI

<17> A_-THRMTRIP

A_PMSYNC

WR82 20/4/1

A_PMDOWN_R

A_-THRMTRIP

WBC123

1n/4/X7R/50V/K

C

3

D14

T7

C15

D13

A15

AF3

PROCPW RGD

RESET#

PM_SYNC

PM_DOW N

PECI

THERMTRIP#

D16

CATERR#

NOA_STBP_1

NOA_STBN_1

NOA_STBP_0

NOA_STBN_0

R35

R34

J37

J36

MBP_N_3

MBP_N_2

MBP_N_1

MBP_N_0

R32

T32

L40

L38

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST

N40

N39

L39

M40

N38

5 OF 12

VCCST

WR26

1K/4/1

LGA1200D

To

DDPB

<48>

<48>

<48>

<48>

<48>

<48>

<48>

<48>

CML_S_IP

<48> DDI1_AUX

<48> DDI1_AUX-

B

To

DDP1

To

DDP2

<54>

<54>

<54>

<54>

<54>

<54>

<54>

<54>

<47>

<47>

<47>

<47>

<47>

<47>

<47>

<47>

F39

F38

G40

G39

H38

H39

J39

J40

DDI1_TX0

DDI1_TX0DDI1_TX1

DDI1_TX1DDI1_TX2

DDI1_TX2DDI1_TX3

DDI1_TX3-

DVI_TX2

DVI_TX2DVI_TX1

DVI_TX1DVI_TX0

DVI_TX0DVI_TXC

DVI_TXC-

HDMI_TX2

HDMI_TX2HDMI_TX1

HDMI_TX1HDMI_TX0

HDMI_TX0HDMI_TXC

HDMI_TXC-

DVI

HDMI

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

K39

K38

DDI1_AUXP

DDI1_AUXN

F35

F36

E36

E37

D37

D38

G36

G37

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

H36

H35

DDI2_AUXP

DDI2_AUXN

A37

B37

C38

B38

D40

C40

E39

E40

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

B36

C36

DDI3_AUXP

DDI3_AUXN

BMAP_REV=1.0

WR47

WR36

WR43

WR46

1K/4/1/X

1K/4/1/X

1K/4/1/X

1K/4/1/X

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXP[2]

EDP_TXN[2]

EDP_TXP[3]

EDP_TXN[3]

M15

M14

N15

N14

L14

L15

L13

K13

EDP_AUXP

EDP_AUXN

K12

K11

EDP_DISP_UTIL

L37

DP_OBS

B39

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

LGA1200C

CML_S_IP

BMAP_REV=1.0

AB39

Bifurcation Config.

1K/4/1/X

1x16

1x16 Reversed

2x8

2x8 Reversed

1x8+2x4

1x8+2x4 Reversed

VCCSTG

VCCST_VCCPLL

M9

N9

M10A_AZ_CPU_SDI_R WR85

20/4/1

PEG_RXP[0]

PEG_RXN[0]

PEG_TXP[0]

PEG_TXN[0]

A8

B8

PA_EXP_TXP0

PA_EXP_TXN0

PA_EXP_RXP1 F11

PA_EXP_RXN1 G11

PEG_RXP[1]

PEG_RXN[1]

PEG_TXP[1]

PEG_TXN[1]

B7

C7

PA_EXP_TXP1

PA_EXP_TXN1

PEG_RXP[2]

PEG_RXN[2]

PEG_TXP[2]

PEG_TXN[2]

A6

A5

PA_EXP_TXP2

PA_EXP_TXN2

PEG_RXP[3]

PEG_RXN[3]

PEG_TXP[3]

PEG_TXN[3]

B5

B4

PA_EXP_TXP3

PA_EXP_TXN3

PA_EXP_RXP3 F9

PA_EXP_RXN3 G9

Signals Lanes

CFG[6] CFG[5] CFG[2]

1

1

1

1

0

0

1

1

0

0

0

0

WR30

51/4/1/X

A_TDO <13>

A_TDI <13>

A_TMS <13>

A_TCK <13>

A_-TRST <10>

A_-HPREQ <12>

A_-HPRDY <12>

A_CPU_ID

WR11

51/4/1

PA_EXP_RXP0 G12

PA_EXP_RXN0 H12

PA_EXP_RXP2 G10

PA_EXP_RXN2 H10

1

0

1

0

1

0

PA_EXP_RXP4 J9

PA_EXP_RXN4 K9

l

a

ti

PA_EXP_RXP5 E7

PA_EXP_RXN5 E6

PA_EXP_RXP6 F6

PA_EXP_RXN6 F5

WR9

51/4/1/X

WR21

8.2K/4/1

WR22

8.2K/4/1/X

PA_EXP_RXP7 G7

PA_EXP_RXN7 G6

PEG_RXP[4]

PEG_RXN[4]

PEG_TXP[4]

PEG_TXN[4]

C4

C3

PA_EXP_TXP4

PA_EXP_TXN4

PEG_RXP[5]

PEG_RXN[5]

PEG_TXP[5]

PEG_TXN[5]

D3

D2

PA_EXP_TXP5

PA_EXP_TXN5

PEG_RXP[6]

PEG_RXN[6]

PEG_TXP[6]

PEG_TXN[6]

E2

E1

PA_EXP_TXP6

PA_EXP_TXN6

PEG_RXP[7]

PEG_RXN[7]

PEG_TXP[7]

PEG_TXN[7]

F3

F2

PA_EXP_TXP7

PA_EXP_TXN7

G2

G1

PA_EXP_TXP8

PA_EXP_TXN8

PA_EXP_RXP8 H5

PA_EXP_RXN8 H6

PEG_RXP[8]

PEG_RXN[8]

PEG_TXP[8]

PEG_TXN[8]

PA_EXP_RXP9 J6

PA_EXP_RXN9 J7

PEG_RXP[9]

PEG_RXN[9]

PEG_TXP[9]

PEG_TXN[9]

H3

H2

PA_EXP_TXP9

PA_EXP_TXN9

PA_EXP_TXP10

PA_EXP_TXN10

PA_EXP_RXP10 K5

PA_EXP_RXN10 K6

PEG_RXP[10]

PEG_RXN[10]

PEG_TXP[10]

PEG_TXN[10]

J2

J1

PA_EXP_RXP11 L6

PA_EXP_RXN11 L7

PEG_RXP[11]

PEG_RXN[11]

PEG_TXP[11]

PEG_TXN[11]

K3

K2

PA_EXP_TXP11

PA_EXP_TXN11

PA_EXP_RXP12 M5

PA_EXP_RXN12M6

PEG_RXP[12]

PEG_RXN[12]

PEG_TXP[12]

PEG_TXN[12]

L2

L1

PA_EXP_TXP12

PA_EXP_TXN12

PA_EXP_RXP13 N6

PA_EXP_RXN13 N7

PEG_RXP[13]

PEG_RXN[13]

PEG_TXP[13]

PEG_TXN[13]

M3

M2

PA_EXP_TXP13

PA_EXP_TXN13

PA_EXP_TXP14

PA_EXP_TXN14

PA_EXP_TXP15

PA_EXP_TXN15

PA_EXP_RXP14 P5

PA_EXP_RXN14 P6

PEG_RXP[14]

PEG_RXN[14]

PEG_TXP[14]

PEG_TXN[14]

N2

N1

PA_EXP_RXP15 R6

PA_EXP_RXN15 R7

PEG_RXP[15]

PEG_RXN[15]

PEG_TXP[15]

PEG_TXN[15]

P3

P2

D

C

A_CPU_ID <30,37,38>

* CPU_ID

1: RKL -->VCCIO=1.0V

0: CML -->VCCIO=0V

N_PCH_VRMPWRGD

DP

SKL_CFG4

SKL_CFG5

SKL_CFG6

SKL_CFG7

3VDUAL

WR27

1K/4/1/X

A_-PROCHOT

1K/4/1/X

K35

L34

CPU-SK/1200/S/GF

VCCSTG

WR54

WR112

100/4/1

1

CFG[13]: 1=VCCSA Fixed Mode / 0=SVID Mode

SKL_CFG2

SKL_CFG13 WR111

2

CFG[4]: 1=eDP enable / 0=eDP disable

CFG[7]: 1=PEG Train immediately following RESET

0=PEG Wait for BIOS

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

PROC_PREQ

PROC_PRDY

CPU_ID

WBC47

1n/4/X7R/50V/K

L35

K36

M35

N35

N37

P36

R36

P37

N34

L36

M37

P34

M38

N36

P38

P39

檢檢模檢檢檢模模

The CFG signals

default value of

'1'

<10> A_DMI_0RXP

<10> A_DMI_0RXN

N_AZCPU_SCLK <13>

N_AZCPU_SDOUT <13>

A_AZ_CPU_SDI <13>

A_DMI_0RXP

A_DMI_0RXN

AD4

AD5

<10> A_DMI_1RXP

<10> A_DMI_1RXN

A_DMI_1RXP AD7

A_DMI_1RXN AD8

<10> A_DMI_2RXP

<10> A_DMI_2RXN

A_DMI_2RXP AC5

A_DMI_2RXN AC6

<10> A_DMI_3RXP

<10> A_DMI_3RXN

A_DMI_3RXP AB6

A_DMI_3RXN AB7

DMI_TXP[0]

DMI_TXN[0]

AF1

AF2

A_DMI_0TXP

A_DMI_0TXN

DMI_RXP[1]

DMI_RXN[1]

DMI_TXP[1]

DMI_TXN[1]

AE2

AE3

A_DMI_1TXP

A_DMI_1TXN

DMI_RXP[2]

DMI_RXN[2]

DMI_TXP[2]

DMI_TXN[2]

AD1

AD2

A_DMI_2TXP

A_DMI_2TXN

A_DMI_3TXP

A_DMI_3TXN

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[3]

DMI_RXN[3]

DMI_TXP[3]

DMI_TXN[3]

AC2

AC3

AA7

AA8

DMI_RXP[4]

DMI_RXN[4]

DMI_TXP[4]

DMI_TXN[4]

AB4

AB3

Y6

Y7

DMI_RXP[5]

DMI_RXN[5]

DMI_TXP[5]

DMI_TXN[5]

AA5

AA4

W5

W6

DMI_RXP[6]

DMI_RXN[6]

DMI_TXP[6]

DMI_TXN[6]

Y4

Y3

V4

V5

DMI_RXP[7]

DMI_RXN[7]

DMI_TXP[7]

DMI_TXN[7]

W3

W2

3 OF 12

A_DMI_0TXP <10>

A_DMI_0TXN <10>

A_DMI_1TXP <10>

A_DMI_1TXN <10>

A_DMI_2TXP <10>

A_DMI_2TXN <10>

A_DMI_3TXP <10>

A_DMI_3TXN <10>

B

<28> PEGX4_RXP0

<28> PEGX4_RXN0

H15

J15

PEGx4_RXP[0]

PEGx4_RXN[0]

PEGx4_TXP[0]

PEGx4_TXN[0]

A12

B12

PEGX4_TXP0 <28>

PEGX4_TXN0 <28>

<28> PEGX4_RXP1

<28> PEGX4_RXN1

E15

F15

PEGx4_RXP[1]

PEGx4_RXN[1]

PEGx4_TXP[1]

PEGx4_TXN[1]

B11

C11

PEGX4_TXP1 <28>

PEGX4_TXN1 <28>

<28> PEGX4_RXP2

<28> PEGX4_RXN2

G14

H14

PEGx4_RXP[2]

PEGx4_RXN[2]

PEGx4_TXP[2]

PEGx4_TXN[2]

C10

D10

PEGX4_TXP2 <28>

PEGX4_TXN2 <28>

<28> PEGX4_RXP3

<28> PEGX4_RXN3

F13

G13

PEGx4_RXP[3]

PEGx4_RXN[3]

PEGx4_TXP[3]

PEGx4_TXN[3]

B9

C9

PEGX4_TXP3 <28>

PEGX4_TXN3 <28>

4 OF 12

PA_EXP_TXP[0..15]

CPU-SK/1200/S/GF

1.2

若若不不CODEC一出出料出,請先先CLK and SDO對對電對。

PA_EXP_TXN[0..15]

A

PA_EXP_RXP[0..15]

PA_EXP_RXN[0..15]

PA_EXP_TXP[0..15] <21>

CPU-SK/1200/S/GF

PA_EXP_TXN[0..15] <21>

A

PA_EXP_RXP[0..15] <21>

PA_EXP_RXN[0..15] <21>

Gigabyte Technology

Title

CPU LGA1200-A

5

4

3

2

Size

Custom

Document Number

Date:

Tuesday, January 26, 2021

Rev

1.0

B560 HD3

Sheet

1

4

of

70

5

4

3

2

CML_S_IP

LGA1200A

SKT_H4

LGA1200B

LGA1200

BMAP_REV=1.0

MDA5

MDA4

MDA7

MDA3

MDA1

MDA0

MDA2

MDA6

MDA8

MDA13

MDA10

MDA14

MDA9

MDA12

MDA15

MDA11

MDA21

MDA20

MDA22

MDA17

MDA19

MDA16

MDA18

MDA23

MDA28

MDA24

MDA31

MDA30

MDA25

MDA29

MDA26

MDA27

MDA36

MDA37

MDA34

MDA38

MDA33

MDA32

MDA35

MDA39

MDA40

MDA45

MDA47

MDA46

MDA41

MDA44

MDA43

MDA42

MDA48

MDA50

MDA52

MDA54

MDA53

MDA51

MDA49

MDA55

MDA56

MDA58

MDA60

MDA62

MDA59

MDA61

MDA63

MDA57

D

C

B

<8> VREF_CA1

<8> VREF_CA0

VREF_CA1

VREF_CA0

AE39

AE38

AH39

AH38

AF40

AE40

AH40

AG40

AK39

AK40

AN39

AM40

AL40

AK38

AN40

AN38

AR39

AR40

AV39

AU40

AR38

AT40

AW 38

AV38

AV36

AY36

AV33

AY34

AY35

AW 36

AY33

AW 33

AW 11

AV11

AY7

AY8

AW 9

AW 10

AV7

AW 7

AW 5

AY5

AW 2

AW 3

AY4

AV5

AV1

AV2

AT1

AN1

AT3

AP1

AT2

AN3

AR1

AN2

AL2

AH1

AL3

AJ1

AH3

AL1

AH2

AK1

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[18]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

AK30

AM32

AJ32

AK32

AL32

AM31

AM30

AL30

DDR0_ECC[7]

DDR0_ECC[6]

DDR0_ECC[5]

DDR0_ECC[4]

DDR0_ECC[3]

DDR0_ECC[2]

DDR0_ECC[1]

DDR0_ECC[0]

AC38

AC40

DDR_VREF_CA_1

DDR_VREF_CA_0

1

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKP[1]

DDR0_CKN[1]

DDR0_CKP[2]

DDR0_CKN[2]

DDR0_CKP[3]

DDR0_CKN[3]

AU24

AV24

AY23

AW 23

AT19

AU19

AY18

AW 18

M_DCLKA0

M_-DCLKA0

M_DCLKA1

M_-DCLKA1

M_DCLKA2

M_-DCLKA2

M_DCLKA3

M_-DCLKA3

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

AY31

AW 31

AV30

AV31

CKEA0

CKEA1

CKEA2

CKEA3

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

AY15

AY13

AV15

AV13

M_-CSA0

M_-CSA1

M_-CSA2

M_-CSA3

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

AY14

AV14

AU14

AT14

MODT_A0

MODT_A1

MODT_A2

MODT_A3

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

AY16

AW 17

SBAA0

SBAA1

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

AV29

AW 29

BG_A0

BG_A1

AV16

AW 16

AU16

MAAA16

MAAA14

MAAA15

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[3]

DDR0_MA[4]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

AU18

AY25

AY24

AW 25

AV25

AY26

AV26

AY27

AW 27

AY28

AU17

AV27

AV28

AW 14

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_PAR

DDR0_ALERT#

AY30

AV18

AY29

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[1]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSN[0]

AJ3

AK3

AP3

AR3

AV3

AV4

AV8

AV9

AV34

AV35

AU38

AT38

AM38

AL38

AG38

AF38

DDR0_DQSP[8]

DDR0_DQSN[8]

1 OF12

CPU-SK/1200/S/GF

CKEA0

CKEA1

CKEA2

CKEA3

MDB4

MDB5

MDB1

MDB6

MDB3

MDB7

MDB0

MDB2

MDB13

MDB8

MDB14

MDB10

MDB9

MDB12

MDB15

MDB11

MDB17

MDB20

MDB22

MDB19

MDB16

MDB21

MDB23

MDB18

MDB28

MDB29

MDB30

MDB27

MDB24

MDB25

MDB31

MDB26

MDB37

MDB33

MDB34

MDB39

MDB36

MDB32

MDB38

MDB35

MDB40

MDB45

MDB42

MDB46

MDB44

MDB41

MDB47

MDB43

MDB52

MDB53

MDB54

MDB48

MDB49

MDB51

MDB55

MDB50

MDB58

MDB60

MDB62

MDB59

MDB57

MDB56

MDB63

MDB61

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

<8>

M_-CSA0

M_-CSA1

M_-CSA2

M_-CSA3

<8>

<8>

<8>

<8>

AD34

AD35

AE36

AF36

AG35

AG34

AD36

AG36

AJ36

AJ35

AL36

AM35

AK36

AJ34

AM36

AM34

AT36

AP36

AT34

AP33

AR36

AT35

AR33

AT33

AP31

AT31

AT29

AP28

AR31

AT30

AR28

AT28

AT12

AR12

AT10

AR10

AP12

AT11

AP10

AN10

AR8

AT8

AT5

AT6

AP8

AT7

AP5

AR5

AM8

AM7

AK6

AM5

AM6

AK7

AK5

AL5

AF7

AH8

AG5

AF6

AH6

AH7

AF5

AH5

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

AM26

AM27

AL28

AK28

AM28

AL26

AK26

AJ28

DDR1_ECC[7]

DDR1_ECC[6]

DDR1_ECC[5]

DDR1_ECC[4]

DDR1_ECC[3]

DDR1_ECC[2]

DDR1_ECC[1]

DDR1_ECC[0]

l

a

ti

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_W E#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR CHANNEL A

M_DCLKA0

M_-DCLKA0

M_DCLKA1

M_-DCLKA1

M_DCLKA2

M_-DCLKA2

M_DCLKA3

M_-DCLKA3

AJ30

AJ31

SBAA0 <8>

SBAA1 <8>

BG_A0 <8>

BG_A1 <8>

M_-ACT_A <8>

M_DDR_PARA <8>

M_-ALERT_A <8>

M_DQSA7

M_-DQSA7

M_DQSA6

M_-DQSA6

M_DQSA5

M_-DQSA5

M_DQSA4

M_-DQSA4

M_DQSA3

M_-DQSA3

M_DQSA2

M_-DQSA2

M_DQSA1

M_-DQSA1

M_DQSA0

M_-DQSA0

<9> VREF_CA3

<9> VREF_CA2

VREF_CA3 AB40

VREF_CA2 AC39

DDR_VREF_CA_3

DDR_VREF_CA_2

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKP[1]

DDR1_CKN[1]

DDR1_CKP[2]

DDR1_CKN[2]

DDR1_CKP[3]

DDR1_CKN[3]

AT23

AU23

AV22

AU22

AT21

AU21

AU20

AV20

M_DCLKB0

M_-DCLKB0

M_DCLKB1

M_-DCLKB1

M_DCLKB2

M_-DCLKB2

M_DCLKB3

M_-DCLKB3

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

AT25

AR26

AT26

AP26

CKEB0

CKEB1

CKEB2

CKEB3

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

AN17

AN15

AR16

AM15

M_-CSB0

M_-CSB1

M_-CSB2

M_-CSB3

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

AM17 MODT_B0

AP14 MODT_B1

AM16 MODT_B2

AM14 MODT_B3

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

AP18

AN19

SBAB0

SBAB1

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

AM23

AM22

BG_B0

BG_B1

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_W E#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

AM18 MAAB16

AP17 MAAB14

AP16 MAAB15

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[3]

DDR1_MA[4]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

AP19

AP20

AR20

AM20

AP21

AN21

AR22

AM21

AP22

AN23

AR18

AP23

AR24

AP15

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_PAR

DDR1_ALERT#

AP25

AM19

AP24

DDR1_DQSP[7]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSN[6]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[0]/DDR0_DQSN[2]

AF8

AG8

AK8

AL8

AP6

AP7

AN11

AN12

AP29

AP30

AP34

AP35

AL34

AK34

AF34

AE34

DDR1_DQSP[8]

DDR1_DQSN[8]

AJ27

AJ26

DDR CHANNEL B

M_DCLKB0

M_-DCLKB0

M_DCLKB1

M_-DCLKB1

M_DCLKB2

M_-DCLKB2

M_DCLKB3

M_-DCLKB3

CKEB0

CKEB1

CKEB2

CKEB3

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

D

<9>

<9>

<9>

<9>

M_-CSB0

M_-CSB1

M_-CSB2

M_-CSB3

<9>

<9>

<9>

<9>

SBAB0 <9>

SBAB1 <9>

BG_B0 <9>

BG_B1 <9>

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

C

M_-ACT_B <9>

M_DDR_PARB <9>

M_-ALERT_B <9>

M_DQSB7

M_-DQSB7

M_DQSB6

M_-DQSB6

M_DQSB5

M_-DQSB5

M_DQSB4

M_-DQSB4

M_DQSB3

M_-DQSB3

M_DQSB2

M_-DQSB2

M_DQSB1

M_-DQSB1

M_DQSB0

M_-DQSB0

B

2 OF 12

CPU-SK/1200/S/GF

<8> MODT_A[0..3]

<9> MODT_B[0..3]

<8> MDA[0..63]

<9> MDB[0..63]

MODT_A[0..3]

MODT_B[0..3]

MDA[0..63]

MDB[0..63]

M_DQSA[0..7]

<8> M_DQSA[0..7]

<8> M_-DQSA[0..7]

A

<8> MAAA[0..16]

黑黑cover

<9> MAAB[0..16]

<9> M_DQSB[0..7]

LGA1200

ILM_BP_CR/1200/BKNI/[12KRC-SF0001-83R_12KRC-SF0001-84R]

<9> M_-DQSB[0..7]

M_-DQSA[0..7]

A

MAAA[0..16]

MAAB[0..16]

M_DQSB[0..7]

Gigabyte Technology

M_-DQSB[0..7]

Title

CPU LGA1200-B

5

4

3

2

Size

Custom

Document Number

Date:

Tuesday, January 26, 2021

Rev

1.0

B560 HD3

Sheet

1

5

of

70

5

4

3

2

1

VCCSA

VCCGT

WBC56

22u/6/X5R/6.3V/M

WBC57

22u/6/X5R/6.3V/M

DCC56

22u/6/X5R/6.3V/M

AA32

AA34

AA35

AA36

AA37

AA38

AB32

AB33

AB34

AB35

AB36

AC32

AD32

AE32

AF32

AG32

R40

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

V32

V33

V34

V36

V38

V40

W 32

W 34

W 35

W 36

W 37

W 38

Y32

Y33

Y34

Y36

Y38

請CPU SOCKET (TOP LAYER)

D

VCCSA

WBC52

47u/8/X5R/6.3V/M/X

請CPU SOCKET (Bottom LAYER)

change footprint to C0805-L-1

VCCIO2

VCCIO2

WBC77

22u/6/X5R/6.3V/M

WBC78

22u/6/X5R/6.3V/M

請CPU SOCKET (TOP LAYER)

VCCIO2

C

WBC70

22u/6/X5R/6.3V/M/X

WBC71

22u/6/X5R/6.3V/M/X

WBC72

22u/6/X5R/6.3V/M

請CPU SOCKET (Bottom LAYER)

VCCIO

LGA1200J

SKT_H4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

AB37

AB38

VCCIO2

AJ9

AK10

AK11

AL10

AL11

VCCIO_1_2

VOUT = 0.95V

IOUT = 9.5A

VCCIO

<30> VCCSA_SENSE

<38> VCCIO2_SENSE

<37> VCCIO_SENSE

AR14

AT24

AU15

AU25

AV17

AV19

AV23

AW 13

AW 15

AW 24

AW 26

AW 28

AW 30

AY17

VCCDDQ_EDGECAP2

VCCDDQ_EDGECAP1

AM13

AM24

l

a

ti

VCCIO_2

VCCIO_2

VCCIO_2

VCCIO_2

VCCIO_2

VCCIO_1

VCCIO_1

VCCIO_1

VCCIO_1

AA3

AB8

AC1

AC7

AD6

U5

V3

V7

W1

W7

W8

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

VCCIO_0

C6

AE4

D5

VCCSA_SENSE

VCCIO_1_2_SENSE

VCCIO_0_SENSE

D6

<30,37> VSSSA_VIO_SENSE

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCDDQ

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

AK25

AL12

AL24

AM12

VCCIO_0

VOUT = 0.95V FOR CML

VOUT = 1.05V FOR RKL

IOUT = 8A

VDDQ

LGA1200

B3

B6

D1

G3

H1

L11

L12

L3

M1

M11

M12

N11

N12

N13

VCCGT_SENSE <30>

VSSGT_SENSE <30>

SKT_H4

LGA1200K

VCCSA

LGA1200

D

+VCCDDQ_EDGECAP2

+VCCDDQ_EDGECAP1

VCCST

WR87

0/4

VCCST

VCCST

VCCST

U2

V1

V2

VCCSFR

R1

VCCSFR

AU13

AU27

VCCSFR_OC

VCCSFR_OC

VCCSTG

VCCSTG

R2

R3

VCCSTG

VCCSTG

VCCFPGM0

VCCFPGM1

VCCFPGM2

R4

T5

T6

VCCSFR_OC

VCCSFR_OC

VCCST_VCCPLL

VCCST

WR125

VCCFPGM

WR104

0/4

0/4

VCCST_VCCPLL

VCCSTG

C

WBC124

1u/4/X5R/6.3V/K

VSS_SA_VCCIO_0_SENSE

VCCSFR_OC

WR86

0/4/X

WR95

0/4

WBC96

47u/8/X5R/6.3V/M

10 OF 12

VDDQ

VCCPLL_OC

CPU-SK/1200/S/GF

CPU-SK/1200/S/GF

10 OF 12

WBC53

22u/6/X5R/6.3V/M

WBC54

22u/6/X5R/6.3V/M

WBC59

22u/6/X5R/6.3V/M

SKT_H4

LGA1200L

LGA1200

請CPU SOCKET (TOP LAYER)

K16

G16

H8

AU32

AN25

B

+VCCDDQ_EDGECAP2

+VCCDDQ_EDGECAP1

WBC75

22u/6/X5R/6.3V/M

P33

R33

J4

L4

WBC76

22u/6/X5R/6.3V/M

請CPU SOCKET (Bottom LAYER)

A_RTCCLK

U4

3VDUAL_PCH

<10> A_SUSCLK

A_SUSCLK

6

4

2

VCCB

B

GND

VCCA

A

DIR

1

3

5

WR114

VCCST_VCCPLL

0/4/X A_RTCCLK

74AVC1T45GW/SC70/S/[10TA1-150145-00R]/X

FIVR_PROBE_ANA_1

FIVR_PROBE_ANA_0

THERMDA2

THERMDC2

AH33

AH32

EXTBGREF

THERMDA1

THERMDC1

D8

F8

DDR_VIEW _1

DDR_VIEW _0

CPU_TRIGGEROUT

CPU_TRIGGERIN

PEG_VIEW _3

PEG_VIEW _2

PE16_AMON2_PEG_VIEW _1

PE16_AMON1_PEG_VIEW _0

P8

M8

PE4_AMON2

PE4_AMON1

G4

E4

DMI_AMON2

DMI_AMON1

J11

J13

CPU_EDM_1

CPU_EDM_0

B15

H_RTCCLK

VCCCOREG5

VCCCOREG4

RSVD_M16

RSVD_M33

RSVD_N4

RSVD_T33

<10> N_CPURTCCLK

WR113

0/4

33/4

B

A_CPU_PCH_TO <11>

N_PCH_CPU_TI <11>

AL18

L33

M16

M33

N4

T33

12 OF 12

CPU-SK/1200/S/GF

*CML增增,RKL才才才才

A

WTP3

D12 A_CPU_PCH_TO_R WR88

E12

A_RTCCLK

A

Gigabyte Technology

Title

CPU LGA1200-C

5

4

3

2

Size

Custom

Document Number

Date:

Tuesday, January 26, 2021

Rev

1.0

B560 HD3

Sheet

1

6

of

70

5

VCORE

D

C

A17

A18

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

AJ12

AJ13

AJ14

AJ15

AJ16

AJ17

AJ18

AJ19

AJ20

AJ21

AJ22

AJ23

AJ24

AK13

AK14

AK15

AK16

AK17

AK18

AK19

AK20

AK21

AK22

AK23

B17

B18

B23

B25

B27

B29

B31

B33

B35

C17

LGA1200I

4

SKT_H4

VCORE

LGA1151

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

D17

D19

D21

D23

D25

D27

D29

D31

D33

D34

D35

E17

E18

E19

E20

E21

E22

E23

E24

E25

E26

E27

E28

E29

E30

E31

E32

E33

E34

F17

F19

F21

LGA1200M

VCORE

LGA1200F

VCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

J34

K17

K19

K21

K23

K25

K27

K29

K31

K32

K33

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L31

L32

M17

M19

M21

M23

M25

M27

M29

M31

M32

N17

N18

N19

N20

N21

N22

N23

N24

N25

N26

N27

N28

N29

N30

N32

VCCCORE_SENSE

VSSCORE_SENSE

B16

C16

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

CPU-SK/1200/S/GF

9 OF 12

2

SKT_H4

LGA1200

F23

F25

F27

F29

F31

F33

G17

G18

G19

G20

G21

G22

G23

G24

G25

G26

G27

G28

G29

G30

G31

G32

G33

G34

H17

H19

H21

H23

H25

H27

H29

H31

H33

J17

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

J32

J33

3

CPU-SK/1200/S/GF

9 OF 12

SKT_H4

LGA1200G

LGA1151

A13

A36

A38

A4

A7

AA33

AA6

AB5

AC34

AC35

AC36

AC4

AC8

AD3

AD33

AD37

AD38

AD39

AD40

AE1

AE33

AE35

AE37

AE5

AE6

AE7

AE8

AF33

AF35

AF37

AF39

AF4

AG1

AG2

AG3

AG33

AG37

AG39

AG4

AG6

AG7

AH34

AH35

AH36

AH37

AH4

AJ11

AJ2

AJ25

AJ29

AJ33

AJ37

AJ38

AJ39

AJ4

AJ40

AJ5

AJ6

AJ7

AJ8

AK12

AK2

AK24

AK27

AK29

SKT_H4

LGA1200H

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK31

AK33

AK35

AK37

AK4

AK9

AL13

AL14

AL15

AL16

AL17

AL19

AL20

AL21

AL22

AL23

AL25

AL27

AL29

AL31

AL33

AL35

AL37

AL39

AL4

AL6

AL7

AL9

AM1

AM10

AM11

AM2

AM25

AM29

AM3

AM33

AM37

AM39

AM4

AM9

AN13

AN14

AN16

AN18

AN20

AN22

AN24

AN26

AN27

AN28

AN29

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN4

AN5

AN6

AN7

AN8

AN9

AP11

AP13

AP2

AP27

AP32

AP37

AP38

AP39

AP4

AP40

AP9

AR11

AR13

AR15

AR17

AR19

AR2

AR21

AR23

AR25

AR27

AR29

AR30

AR32

AR34

AR35

AR37

AR4

AR6

AR7

AR9

AT13

AT15

AT16

AT17

AT18

AT20

AT22

AT27

AT32

AT37

AT39

AT4

AT9

AU1

AU10

AU11

AU12

AU2

AU26

AU28

AU29

AU3

AU30

AU31

AU33

AU34

AU35

AU36

AU37

AU39

AU4

AU5

AU6

AU7

SKT_H4

LGA1151

LGA1151

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

l

a

i

t

n

e

d

i

f

n y

o

C

p

o

e

t

C

y

t

b

o

a

n

g

i

G Do

VCORE_VCC_SEN <30>

VCORE_VSS_SEN <30>

1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AU8

AU9

AV10

AV12

AV21

AV32

AV37

AV6

AW 12

AW 32

AW 34

AW 35

AW 37

AW 4

AW 6

AW 8

AY12

AY3

AY32

AY6

B10

B24

B26

B28

B30

B32

B34

C12

C13

C2

C37

C39

C5

C8

D11

D15

D18

D20

D22

D24

D26

D28

D30

D32

D36

D39

D4

D7

D9

E10

E11

E13

E14

E16

E3

E35

E38

E5

E8

E9

F1

F10

F12

F14

F16

F18

F20

F22

F24

F26

F28

F30

F32

F34

F37

F4

F40

F7

G15

G35

G38

G5

G8

H11

H13

H16

H18

H20

H22

H24

H26

H28

H30

H32

H34

H37

H4

H40

H7

H9

J10

J12

J14

J16

J3

J35

J38

J5

J8

K1

K10

K14

K15

K18

K20

K22

K24

K26

K28

K30

K34

K37

K4

K40

K7

K8

L10

L16

L5

L8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L9

M13

M18

M20

M22

M24

M26

M28

M30

M34

M36

M39

M4

M7

N10

N16

N3

N33

N5

N8

P1

P32

P35

P4

P40

P7

R37

R38

R39

R5

R8

T2

T34

T35

T36

T8

U3

U32

U4

U6

V35

V37

V39

V6

V8

W 33

W4

Y35

Y37

Y5

Y8

D

C

8 OF 12

CPU-SK/1200/S/GF

B

B

6 OF 12

CPU-SK/1200/S/GF

CPU-SK/1200/S/GF

7 OF 12

A

A

Gigabyte Technology

Title

CPU LGA1200-D

5

4

3

2

Size

Custom

Document Number

Date:

Tuesday, January 26, 2021

Rev

1.0

B560 HD3

Sheet

1

7

of

70

8

7

6

5

4

DDR4_A1

3

2

1

DDR4_A2

VDDQ

Rev:0.1

77

221

VTT

VTT

RFU

RFU

RFU

2

4

6

9

11

13

15

17

20

22

24

26

28

31

33

35

37

39

42

44

46

48

50

53

55

57

94

96

98

101

103

105

107

109

112

114

116

118

120

123

125

127

129

131

134

136

138

147

149

151

154

156

158

160

162

165

167

169

171

173

176

178

180

182

184

187

189

191

193

195

198

200

202

239

241

243

246

248

250

252

254

257

259

261

263

265

268

270

272

274

276

279

281

283

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC2_SAVE*1

59

61

64

67

70

73

76

80

83

85

88

90

92

204

206

209

212

215

217

220

223

226

229

231

233

236

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

142

143

286

287

288

VPP

VPP

VPP

VPP

VPP

1

145

12V3_NC

12V3_NC

146

VREFCA

284

238

140

139

285

141

VDDSPD

SA2_RFU

SA1

SA0

SDA

SCL

224

81

207

63

BA1

BA0

BG1

BG0

<5> M_-DCLKA1

<5> M_DCLKA1

<5> M_-DCLKA0

<5> M_DCLKA0

219

218

75

74

CK1/NU*

CK1/NU

CK0*

CK0

<5> M_-CSA1

<5> M_-CSA0

235

237

93

89

84

<5> CKEA1

<5> CKEA0

DDRVTT

D

MODT_A[0..3]

<5> MODT_A[0..3]

MDA[0..63]

<5> MDA[0..63]

MAAA[0..16]

<5> MAAA[0..16]

M_DQSA[0..7]

<5> M_DQSA[0..7]

M_-DQSA[0..7]

<5> M_-DQSA[0..7]

C

VDDQ

B

VPP_25V

MAC11

1u/4/X5R/6.3V/K

MAC16

VREF_DDRA0

0.1u/4/X7R/16V/K

VPP_25V

<9,17,63,64,67>

<9,17,63,64,67>

SMB_SW_SD0

SMB_SW_SC0

<5>

<5>

<5>

<5>

<5> MAAA[0..16]

A

MA0_SA2

MA0_SA1

MA0_SA0

SMB_SW_SD0

SMB_SW_SC0

SBAA1

SBAA0

BG_A1

BG_A0

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MAAA16

ODT1

ODT0

PARITY

RESET*

EVENT*

ALERT*

ACT*

DDRVTT

VDDQ

230

91

87

222

58

78

208

62

MODT_A1

MODT_A0

CH_A0

49

194

56

201

47

192

54

199

DQS0

DQS0*

153

152

M_DQSA0

M_-DQSA0

DQS1

DQS1*

164

163

M_DQSA1

M_-DQSA1

DQS2

DQS2*

175

174

M_DQSA2

M_-DQSA2

DQS3

DQS3*

186

185

M_DQSA3

M_-DQSA3

DQS4

DQS4*

245

244

M_DQSA4

M_-DQSA4

DQS5

DQS5*

256

255

M_DQSA5

M_-DQSA5

DQS6

DQS6*

267

266

M_DQSA6

M_-DQSA6

DQS7

DQS7*

278

277

M_DQSA7

M_-DQSA7

DQS8

DQS8*

197

196

DM0/DQS9_DBI0

NC/DQS9*

7

8

DM1/DQS10_DBI1

NC/DQS10*

18

19

DM2/DQS11_DBI2

NC/DQS11*

29

30

DM3/DQS12_DBI3

NC/DQS12*

40

41

DM4/DQS13_DBI4

NC/DQS13*

99

100

DM5/DQS14_DBI5

NC/DQS14*

110

111

DM6/DQS15_DBI6

NC/DQS15*

121

122

DM7/DQS16_DBI7

NC/DQS16*

132

133

DM8/DQS17_DBI8

NC/DQS17*

51

52

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

5

150

12

157

3

148

10

155

16

161

23

168

14

159

21

166

27

172

34

179

25

170

32

177

38

183

45

190

36

181

43

188

97

242

104

249

95

240

102

247

108

253

115

260

106

251

113

258

119

264

126

271

117

262

124

269

130

275

137

282

128

273

135

280

MODT_A1 <5>

MODT_A0 <5>

M_DDR_PARA <5>

-DDR3_RST <9,10>

MAR19

240/4/1

M_-ALERT_A <5>

M_-ACT_A <5>

CB0_NC

CB1_NC

CB2_NC

CB3_NC

CB4_NC

CB5_NC

CB6_NC

CB7_NC

77

221

VTT

VTT

RFU

RFU

RFU

2

4

6

9

11

13

15

17

20

22

24

26

28

31

33

35

37

39

42

44

46

48

50

53

55

57

94

96

98

101

103

105

107

109

112

114

116

118

120

123

125

127

129

131

134

136

138

147

149

151

154

156

158

160

162

165

167

169

171

173

176

178

180

182

184

187

189

191

193

195

198

200

202

239

241

243

246

248

250

252

254

257

259

261

263

265

268

270

272

274

276

279

281

283

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC2_SAVE*1

59

61

64

67

70

73

76

80

83

85

88

90

92

204

206

209

212

215

217

220

223

226

229

231

233

236

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

142

143

286

287

288

VPP

VPP

VPP

VPP

VPP

ODT1

ODT0

PARITY

RESET*

EVENT*

ALERT*

ACT*

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

VDDQ

VPP_25V

1

145

12V3_NC

12V3_NC

146

VREFCA

MA1_SA2

MA1_SA1

MA1_SA0

SMB_SW_SD0

SMB_SW_SC0

284

238

140

139

285

141

VDDSPD

SA2_RFU

SA1

SA0

SDA

SCL

224

81

207

63

BA1

BA0

BG1

BG0

<5> M_-DCLKA3

<5> M_DCLKA3

<5> M_-DCLKA2

<5> M_DCLKA2

219

218

75

74

CK1/NU*

CK1/NU

CK0*

CK0

C_2_NC

S3_N_C

S2_N_C

S1_N

S0_N

<5> M_-CSA3

<5> M_-CSA2

235

237

93

89

84

C_2_NC

S3_N_C

S2_N_C

S1_N

S0_N

203

60

CKE1

CKE0

<5> CKEA3

<5> CKEA2

203

60

CKE1

CKE0

79

72

216

71

214

213

69

211

68

66

225

210

65

232

228

86

82

234

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14_WE*

A15_CAS*

A16_RAS*

A17_NC

79

72

216

71

214

213

69

211

68

66

225

210

65

232

228

86

82

234

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14_WE*

A15_CAS*

A16_RAS*

A17_NC

MAC42

0.1u/4/X7R/16V/K

MAC43

0.1u/4/X7R/16V/K

VPP_25V

<9,17,63,64,67>

<9,17,63,64,67>

SMB_SW_SD0

SMB_SW_SC0

<5>

<5>

<5>

<5>

SBAA1

SBAA0

BG_A1

BG_A0

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

MAAA16

<5> MAAA[0..16]

MA0_SA0

MA0_SA1

MA0_SA2

* 移則 short pad

BLK

* 黑黑 雙雙雙

7

227

205

144

VDDQ

230

MODT_A3

MODT_A2

91

87

222

58

78

208

62

CH_A1

MODT_A3 <5>

MODT_A2 <5>

M_DDR_PARA <5>

-DDR3_RST <9,10>

MABC4

0.1u/4/X7R/16V/K

49

194

56

201

47

192

54

199

DQS0

DQS0*

153

152

M_DQSA0

M_-DQSA0

DQS1

DQS1*

164

163

M_DQSA1

M_-DQSA1

DQS2

DQS2*

175

174

M_DQSA2

M_-DQSA2

DQS3

DQS3*

186

185

M_DQSA3

M_-DQSA3

DQS4

DQS4*

245

244

M_DQSA4

M_-DQSA4

DQS5

DQS5*

256

255

M_DQSA5

M_-DQSA5

DQS6

DQS6*

267

266

M_DQSA6

M_-DQSA6

DQS7

DQS7*

278

277

M_DQSA7

M_-DQSA7

DQS8

DQS8*

197

196

MR23

<5>

MR24

24.9/4/1

MAR117

2K/4/1

Footprint :R0402-2-SHORT20

VREF_DDRA1

MR27

MAR118

2K/4/1

2.2/4

VREF_CA1

<5>

MC21

0.022u/4/X7R/25V/K

比公 2ohm

D

MR28

24.9/4/1

l

a

ti

VDDQ Decouple

VDDQ

VDDQ

MABC18

1u/4/X5R/6.3V/K

MABC38

0.1u/4/X7R/16V/K

MABC15

0.1u/4/X7R/16V/K

MABC39

0.1u/4/X7R/16V/K

MABC11

0.1u/4/X7R/16V/K

MASC3

1u/4/X5R/6.3V/K

VDDQ

VDDQ

MASC4

0.1u/4/X7R/16V/K

MABC37

1u/4/X5R/6.3V/K

MASC1

1u/4/X5R/6.3V/K

MABC34

1u/4/X5R/6.3V/K

MASC2

1u/4/X5R/6.3V/K

VDDQ

MABC35

1u/4/X5R/6.3V/K

MABC10

22u/6/X5R/6.3V/M

DM0/DQS9_DBI0

NC/DQS9*

7

8

DM1/DQS10_DBI1

NC/DQS10*

18

19

DM2/DQS11_DBI2

NC/DQS11*

29

30

DM3/DQS12_DBI3

NC/DQS12*

40

41

DM4/DQS13_DBI4

NC/DQS13*

99

100

DM5/DQS14_DBI5

NC/DQS14*

110

111

DM6/DQS15_DBI6

NC/DQS15*

121

122

MABC19

MABC20

0.47U/2/X5R/6.3V/K

1u/4/X5R/6.3V/K

DM7/DQS16_DBI7

NC/DQS16*

132

133

MABC14

MABC30

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

DM8/DQS17_DBI8

NC/DQS17*

51

52

MABC13

MABC12

MABC16

0.47U/2/X5R/6.3V/K

1u/4/X5R/6.3V/K

1u/4/X5R/6.3V/K

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VDDQ

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

5

150

12

157

3

148

10

155

16

161

23

168

14

159

21

166

27

172

34

179

25

170

32

177

38

183

45

190

36

181

43

188

97

242

104

249

95

240

102

247

108

253

115

260

106

251

113

258

119

264

126

271

117

262

124

269

130

275

137

282

128

273

135

280

MABC17

1u/4/X5R/6.3V/K

MABC21

1u/4/X5R/6.3V/K

MABC8

2.2u/4/X5R/6.3V/M

VDDQ

DDRVTT Decouple

DDRVTT

DDRVTT

MABC25

0.1u/4/X7R/16V/K

MABC24

1u/4/X5R/6.3V/K

MABC28

0.1u/4/X7R/16V/K

若 Power source 端 PWM IC

已若已請 , 則料則則

B

VDDQ

VDDQ

MABC56

22u/6/X5R/6.3V/M

MABC57

22u/6/X5R/6.3V/M

MABC58

22u/6/X5R/6.3V/M

MABC59

22u/6/X5R/6.3V/M

MABC60

22u/6/X5R/6.3V/M

MABC61

22u/6/X5R/6.3V/M

MABC62

22u/6/X5R/6.3V/M

MABC41

0.1u/4/X7R/16V/K

MABC42

0.1u/4/X7R/16V/K

MABC43

0.1u/4/X7R/16V/K

MABC44

0.1u/4/X7R/16V/K

MABC45

0.1u/4/X7R/16V/K

MABC46

0.1u/4/X7R/16V/K

MABC47

0.1u/4/X7R/16V/K

MABC48

0.1u/4/X7R/16V/K

MABC49

0.1u/4/X7R/16V/K

MABC50

0.1u/4/X7R/16V/K

VDDQ

MABC51

0.1u/4/X7R/16V/K

MABC52

0.1u/4/X7R/16V/K

MABC53

0.1u/4/X7R/16V/K

MABC54

0.1u/4/X7R/16V/K

MABC55

0.1u/4/X7R/16V/K

比比比比一請已請

Capture Value

SOC series

黑黑

UD series

橘黑

SMD

SMD

黑黑

DDR4/288/BK/VA/S/G15/4ROW/LONG

DDR4/288/OR/VA/S/G15/4ROW/LONG

深深黑

DDR4/288/BK/VA/D/G15/ONE LATCH/LONG

DDR4/288/GY/VA/D/G15/ONE LATCH/LONG

Gaming series

黑黑

鮮鮮

DDR4/288/BK/VA/D/G15/ONE LATCH/LONG

DDR4/288/RE/VA/D/G15/ONE LATCH/LONG

G1.Sniper

黑黑

綠黑

DDR4/288/BK/VA/D/G15/ONE LATCH/LONG

DDR4/288/GE/VA/D/G15/ONE LATCH/LONG

A

VPP_25V

Gigabyte Technology

Title

DDR4 CHANNEL A

Size

Document Number

Custom

Footprint : DDR4-288P-STH-34C22P-3

4

MABC9

22u/6/X5R/6.3V/M

MABC22

1u/4/X5R/6.3V/K

MABC23

0.1u/4/X7R/16V/K

CHANNEL A1

SA2:0=001

GY

C

若 Power source 端 PWM IC

已若已請 , 則料則則

VDDQ

MA1_SA0

MA1_SA1

MA1_SA2

VDDQ

MABC36