BTL xung số Haui Nhom 13 Thiết kế mạch điều khiển đèn LED sáng lan tắt dần với chiều dài L = 10 sử dụng JK – FF

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (1.26 MB, 26 trang )

TRƯỜNG CƠ KHÍ – Ơ TƠ

KHOA CƠ ĐIỆN TỬ

----------------------

ĐỒ ÁN MÔN HỌC

KỸ THUẬT XUNG – SỐ

Đề Tài: Thiết kế mạch điều khiển đèn LED sáng lan tắt dần với chiều

dài L = 10 sử dụng JK – FF.

Giáo viên hướng dẫn: ThS. Hà Thị Phương

Sinh viên thực hiện:

Phạm Thế Cảnh

2020602053

Đoàn Phi Hùng

2021603240

Hoàng Duy Huy

2021605072

Hà Nội, tháng 12 năm 2023

TRƯỜNG CƠ KHÍ – Ơ TƠ

KHOA CƠ ĐIỆN TỬ

----------------------

ĐỒ ÁN MÔN HỌC

KỸ THUẬT XUNG – SỐ

Đề Tài: Thiết kế mạch điều khiển đèn LED sáng lan tắt dần với chiều

dài L = 10 sử dụng JK – FF.

Giáo viên hướng dẫn: ThS. Hà Thị Phương

Sinh viên thực hiện:

Phạm Thế Cảnh

2020602053

Đoàn Phi Hùng

2021603240

Hoàng Duy Huy

2021605072

Hà Nội, tháng 12 năm 2023

i

LỜI MỞ ĐẦU

Ngày nay cùng với sự tiến bộ của khoa học kĩ thuật, công nghệ điện tử đã đang

và sẽ phát triển ngày càng rộng rãi, đặc biệt là trong kĩ thuật số. Mạch số được ứng

dụng nhiều trong kỹ thuật cũng như đời sống của xã hội. Các ứng dụng của mạch số

như đèn giao thông, đo tốc độ động cơ, đồng hồ số, mạch đếm sản phẩm… Mục đích

của tập đồ án này là thiết kế được mạch điều khiển LED sáng lan tắt dần với chiều

dài L=10 sử dụng JK-FF

Đồ án hồn thành giúp em có được nhiều kiến thức hơn về môn học và giúp

em được tiếp xúc với một phương pháp làm việc mới chủ động hơn, linh hoạt hơn

đặc biệt là làm việc nhóm. Q trình thực hiện đồ án này thật sự bổ ích cho bản thân

em về nhiều mặt. Vì kiến thức và khả năng còn hạn chế, kinh nghiệm còn yếu nên

khơng tránh khỏi những sai sót, rất mong sự đóng góp của thầy cơ và các bạn.

Xin chân thành cảm ơn!

ii

MỤC LỤC

MỤC LỤC ...................................................................................................... III

DANH MỤC HÌNH ẢNH ............................................................................. IV

DANH MỤC BẢNG BIỂU ............................................................................. V

CHƯƠNG 1: TỔNG QUAN BỘ ĐẾM ........................................................6

1.1

KHÁI NIỆM, PHÂN LOẠI ........................................................................6

1.1.1

Khái niệm ....................................................................................6

1.1.2

Đồ hình trạng Thái: ....................................................................6

1.1.3

Phân loại .....................................................................................7

CHƯƠNG 2: TÍNH TỐN THIẾT KẾ MƠ PHỎNG MẠCH .................9

2.1

THIẾT KẾ BỘ ĐẾM.................................................................................9

2.2

TÍNH TỐN .........................................................................................10

2.3

MƠ PHỎNG .........................................................................................17

2.4

THIẾT KẾ SƠ ĐỒ NGUYÊN LÝ ..............................................................18

2.4.1

Các linh kiện chính trong mạch ................................................18

2.4.2

Khối tạo xung - IC555 ...............................................................19

2.4.3

Khối Trigger JK – IC 74LS73 ...................................................21

CHƯƠNG 3: CHẾ TẠO, LẮP RÁP, THỬ NGHIỆM VÀ HIỆU CHỈNH

22

3.1

THIẾT KẾ MẠCH IN .............................................................................22

3.2

CHẾ TẠO, LẮP RÁP .............................................................................22

3.3

THỬ NGHIỆM VÀ HIỆU CHỈNH.............................................................23

CHƯƠNG 4: ĐÁNH GIÁ, KẾT LUẬN ....................................................24

4.1

ĐÁNH GIÁ SẢN PHẨM .........................................................................24

4.2

TÍNH THỰC THẾ CỦA SẢN PHẨM.........................................................24

4.3

ĐỀ XUẤT CẢI TIẾN VÀ HƯỚNG PHÁT TRIỂN ........................................24

TÀI LIỆU THAM KHẢO .............................................................................25

iii

DANH MỤC HÌNH ẢNH

Hình 1.1: Bộ đếm ...............................................................................................6

Hình 1.2: Đồ hình mơ tả hoạt động của bộ đếm ................................................6

Hình 2.1: Sơ đồ mạch đếm .................................................................................9

Hình 2.2: Đồ hình trạng thái .............................................................................10

Hình 2.3: Sơ đồ logic........................................................................................10

Hình 2.4: Đồ hình trạng thái và mã hóa mạch 10 bit .......................................11

Hình 2.5: Đồ hình trạng thái và mã hóa mạch 4 bit .........................................11

Hình 2.6: Sơ đồ logic 4 bit ...............................................................................14

Hình 2.7: Sơ đồ logic mạch 10 bit ....................................................................17

Hình 2.8: Mạch mơ phỏng trên Proteus ...........................................................17

Hình 2.9: Sơ đồ mạch nguyên lý ......................................................................18

Hình 2.10: Khối tạo xung – IC555 ...................................................................19

Hình 2.11: Khối Trigger JK – IC 74LS73 ........................................................21

Hình 3.1: Mạch in 2D .......................................................................................22

Hình 3.2: Mạch in 3D .......................................................................................22

Hình 3.3: Chuẩn bị làm mạch ...........................................................................22

Hình 3.4: Mạch in hồn thiện ...........................................................................23

Hình 3.5: Mạch chạy đáp ứng yêu cầu đề bài ..................................................23

iv

DANH MỤC BẢNG BIỂU

Bảng 2-1: Chuyển đổi trạng thái và các đầu vào kích 4 bit .............................12

Bảng 2-2: Karnough J1 .....................................................................................12

Bảng 2-3: Karnough K1 ....................................................................................12

Bảng 2-4: Karnough J2 .....................................................................................13

Bảng 2-5: Karnough K2 ....................................................................................13

Bảng 2-6: Karnough J3 .....................................................................................13

Bảng 2-7: Karnough K3 ....................................................................................13

Bảng 2-8: Karnough J4 .....................................................................................14

Bảng 2-9: Karnough K4 ....................................................................................14

Bảng 2-10: Bảng chuyển đổi trạng thái 10 bit .................................................15

Bảng 2-11: Bảng giá trị các đầu vào kích 10 bit ..............................................16

Bảng 2-12: Bảng linh kiện sử dụng trong mạch ...............................................19

v

CHƯƠNG 1: TỔNG QUAN BỘ ĐẾM

1.1

Khái niệm, phân loại

Mạch đếm là một mạch dãy đơn giản được xây dựng từ các phần tử nhớ và các

phần tử tổ hợp. Mạch đếm là thành phần cơ bản của các hệ thống số, chúng được sử

dụng để đếm.

1.1.1 Khái niệm

Bộ đếm là một mạch dãy tuần hồn có một đầu vào đếm và một đầu ra, mạch có

số trạng thái trong chính hệ số đếm - Kđ

Dưới tác động của tín hiệu vào đếm mạch sẽ chuyển từ trạng thái trong này đến

một trạng thái trong khác thoe một thứ tự nhất định. Cứ sau Kđ lần tín hiệu vào đếm,

mạch sẽ trở về trạng thái xuất phát ban đầu.

Bộ đếm thực hiện việc đếm các dãy xung khi có xung điều khiển và nó chỉ có một

đầu vào. Do đó, nếu xung đồng bộ CLK xuất hiện khác thời điểm xung đếm Xđ xuất

hiện thì việc đếm xung khơng thực hiện được nên mạch đếm phải có xung đếm đưa vào

chính là dãy xung đồng bộ hay mạch đếm chỉ có một đầu vào.

Hình 1.1: Bộ đếm

1.1.2 Đồ hình trạng Thái:

Đồ hình là mơ hình mơ tả sự chuyển đổi các trạng thái trong hay chính là mơ tả

hoạt động của bộ đếm.

Hình 1.2: Đồ hình mơ tả hoạt động của bộ đếm

6

Khi khơng có tín hiệu vào đếm (𝑋đ ) mạch giữ ngun trạng thái ban đầu (i i) khi

có tín hiệu vào đếm (𝑋đ ) mạch sẽ chuyển đến trạng thái kế tiếp(i →i+1).

Khi bộ đếm ở trạng thái SKđ-1 nếu tác động một tín hiệu vào đếm thì bộ đếm sẽ

trở vềtrạng thái ban đầu 𝑆0 và khi đó đồng thời xuất hiện tín hiệu ra một lần duy nhất.

Trong trường hợp cần hiển thị trạng thái của bộ đếm thì phải dùng thêm mạch

giải mã.

1.1.3 Phân loại

Có nhiều cách phân loại bộ đếm:

-

Phân loại theo cách làm việc:

+ Bộ đếm đồng bộ (Synchronous counter): là bộ đếm mà sự chuyển đổi trạng thái

trong các FF diễn ra đồng thời khi có tác động của xung đếm. Mọi sự chuyển đổi trạng

thái (từ Si sang trạng thái mới Sj) đều không thông qua trạng thái trung gian.

Xung đồng bộ tác động đồng thời tới các phần tử nhớ.

+ Bộ đếm không đồng bộ (Asynchronous counter): là bộ đếm tồn tại ít nhất một

cặp chuyển biến trạng thái Si→Sj mà trong đó các FF khơng thay đổi trạng thái đồng

thời.

Xung đồng bộ tác động không đồng thời tới các FF.

-

Phân loại theo hệ số đếm.

+ Bộ đếm có hệ số đếm 𝐾đ = 2𝑛 : Bộ đếm có hệ số đếm cực đại, khi sử dụng n

FF để mã hoá các trạng thái trong cho bộ đếm thì khả năng mã hoá tối đa.

(Kđ = 2, 4, 8, 16...)

+ Bộ đếm có hệ số đếm 𝐾đ ≠ 2𝑛 : Sử dụng n FF để mã hoá các trạng thái trong

cho bộ đếm, sẽ có (2𝑛 − 𝐾đ ) trạng thái không được sử dụng đến. Do vậy khi thiết kế bộ

đếm cần phải lưu ý đến các trạng thái không sử dụng tức là cần phải có biện pháp làm

cho bộ đếm thốt khỏi các trạng thái đó một cách hợp lý để trở về chu trình đúng mà

vẫn phải đảm bảo bộ đếm được thiết kế là đơn giản.

(Kđ = 3, 5, 6, 7, 10...)

-

Phân loại theo mã:

+ Quá trình đếm của bộ đếm là quá trình thay đổi từ trạng thái trong này đến trạng

thái trong khác và mỗi trạng thái trong của bộ đếm được mã hoá bởi một mã cụ thể.

7

Cùng một bộ đếm có thể có nhiều cách mã hoá trạng thái trong khác nhau, các cách mã

hoá khác nhau sẽ tương ứng với các mạch thực hiện khác nhau.

• Mã nhị phân, Mã Gray

• Mã BCD, Mã Johnson

• Mã vòng...

-

Phân loại theo hướng đếm:

+ Bộ đếm thuận (Up counter): là bộ đếm mà khi có tín hiệu vào đếm (Xđ) thì trạng

thái trong của bộ đếm tăng lên 1. (Si→Si+1)

+ Bộ đếm nghịch (Down counter): là bộ đếm mà khi có tín hiệu vào đếm (Xđ) thì

trạng thái trong của bộ đếm giảm đi 1. (Si→Si-1)

Chú ý: Khái niệm thuận nghịch chỉ là tương đối chủ yếu là do vấn đề mã hoá các

trạng thái trong của bộ đếm.

+ Bộ đếm thuận nghịch: là bộ đếm vừa có khả năng đếm thuận vừa có khả năng

đếm nghịch.

+ Bộ đếm có khả năng lập trình: Kđ có thể thay đổi phụ thuộc vào tín hiệu điều

khiển.

+ Bộ đếm khơng có khả năng lập trình: Kđ cố định, khơng thay đổi được

8

CHƯƠNG 2: TÍNH TỐN THIẾT KẾ MƠ PHỎNG MẠCH

2.1

Thiết kế bộ đếm

Khối nguồn

Khối tạo

xung

Khối đếm

Khối LED

hiển thị

Hình 2.1: Sơ đồ mạch đếm

Để thiết kế bộ đếm ta tiến hành theo các bước sau:

Bước 1:

+ Xác định các yêu cầu của bài tốn

+ Phân tích u cầu đầu bài tìm ra số trạng thái trong.

Bước 2:

+ Lập đồ hình trạng thái

Căn cứ vào yêu cầu của bộ đếm cần thiết kế như: hệ số đếm và một số các yêu

cầu khác để xây dựng đồ hình mơ tả hoạt động của bộ đếm.

Bước 3:

+ Xác định số phần tử nhớ cần sử dụng, mã hóa các trạng thái trongcủa bộ đếm

theo mã đã cho.

Số phần tử nhớ được xác định như sau:

- Mã nhị phân và mã Gray n ≥ log2 Kđ

- Mã vòng n = Kđ

- Mã Johnson n = 1/2 Kđ

Bước 4:

+ Xác định hàm kích của các FF và hàm ra:

Dựa vào bảng chuyển đổi trạng thái, bảng ra để xác định phương trình kích cho

các FF và phương trình hàm ra.

Bước 5:

+ Vẽ sơ đồ mạch thực hiện

Từ các phương trình đầu vào kích các FF và phương trình hàm ra đưa ra sơ đồ

mạch thực hiện.

9

2.2

Tính tốn

Với khối nguồn ta lựa chọn sử dụng nguồn một chiều từ 5-9 V từ sạc điện thoại

hay pin dự phòng, 10 LED màu xanh lá mạ hiển thị sáng tắt dần và khối tạo xung 555

đã có cơng thức là : 𝐹 =

1,44

(𝑅1 +2𝑅2 )𝐶1

Nên phần tính tốn ta chú tâm vào khối đếm

+Flip-flop sử dụng

Là JK-FF là phần tử có hai đầu vào điều khiển và hai đầu ra đầu vào J đóng vai

trị thiết lập, đầu K đóng vai trị xóa.

0X

X0

1X

0

0

X1

Hình 2.2: Đồ hình trạng thái

JK=00 FF giữ nguyên trạng thái cũ

JK=01 FF luôn chuyển đến trạng thái 0

JK=10 FF luôn chuyển đến trạng thái 1

JK=11 FF đảo trạng thái

J

Q

̅

𝑄

K

Hình 2.3: Sơ đồ logic

̅̅̅̅

̅

Phương trình đặc trưng: 𝑄𝑛+1 = 𝐽𝑄

𝑛 + 𝐾 𝑄𝑛

+ Xác định số phần tử nhớ cần sử dụng

Với mạch điều khiển LED sáng lan tắt dần với chiều dài L=10, tồn tại 20 trạng

thái. Do đó số phần tử nhớ cần sử dụng là:

1

Mã Johnson 𝑛 = ; 𝐾đ = 10

2

Cần sử dụng 10 phần tử nhớ

10

+ Đồ hình trạng thái:

Hình 2.4: Đồ hình trạng thái và mã hóa mạch 10 bit

Mạch đếm vịng có thể lập số flip-flop không hạn chế và để thuận tiện tính tốn

thì ta xét với 4bit với 8 trạng thái sáng tắt của LED. Ở trường hợp này cần dùng 4 FF.

Hình 2.5: Đồ hình trạng thái và mã hóa mạch 4 bit

+ Lập bảng chuyển đổi trạng thái và giá trị các đầu vào kích 4bit xếp theo mã gray

Q4

Q3

Q2

Q1

Q`4 Q`3 Q`2 Q`1 J4 K4 J3 K3 J2 K2 J1 K1

0

0

0

0

1

0

0

0

1

X

0

X

0

X

0

0

0

0

1

0

0

0

0

0

X

0

X

0

X

X 1

0

0

1

1

0

0

0

1

0

X

0

X

X 1

X 0

0

0

1

0

X

X

X

X

X X

X X

X X

X X

0

1

1

0

X

X

X

X

X X

X X

X X

X X

0

1

1

1

0

0

1

1

0

X

X 1

X 0

X 0

0

1

0

1

X

X

X

X

X X

X X

X X

X X

0

1

0

0

X

X

X

X

X X

X X

X X

X X

1

1

0

0

1

1

1

0

0

X 0

1

0 X

11

X

X

X

1

1

0

1

X

X

X

X

X X

X X

X X

X X

1

1

1

1

0

1

1

1

X 1

X 0

X 0

X 0

1

1

1

0

1

1

1

1

X 0

X 0

X 0

1

1

0

1

0

X

X

X

X

X X

X X

X X

X X

1

0

1

1

X

X

X

X

X X

X X

X X

X X

1

0

0

1

X

X

X

X

X X

X X

X X

X X

1

0

0

0

1

1

0

0

X 0

1

0

0

X

X

Bảng 2-1: Chuyển đổi trạng thái và các đầu vào kích 4 bit

Dùng bảng Karnough để rút gọn và xác định phương trình đầu vào kích.

Ta có:

Q2 Q1

Bảng 2-2: Karnough J1

J1

00

01

11

10

00

0

X

X

X

01

X

X

X

X

11

0

X

X

1

10

0

X

X

X

Q4Q3

Q2 Q1

K1

Q4Q3

J1=Q2

Bảng 2-3: Karnough K1

00

01

11

10

00

X

1

0

X

01

X

X

0

X

11

X

X

0

X

10

X

X

X

X

12

̅̅̅2

𝐾1 = 𝑄

X

X

Q2 Q1

J2

Q4Q3

00

01

11

10

00

0

0

X

X

01

X

X

X

X

11

1

X

X

X

10

0

X

X

X

Q2 Q1

K2

Q4Q3

01

11

10

00

X

X

1

X

01

X

X

0

X

11

X

X

0

0

10

X

X

X

X

Q2 Q1

Q4Q3

𝐾1 = ̅̅̅̅

𝑄3

Bảng 2-6: Karnough J3

00

01

11

10

00

0

0

0

X

01

X

X

X

X

11

X

X

X

X

10

1

X

X

X

Q2 Q1

K3

J2=Q3

Bảng 2-5: Karnough K2

00

J3

Q4Q3

Bảng 2-4: Karnough J2

J3=Q4

Bảng 2-7: Karnough K3

00

01

11

10

00

X

X

X

X

01

X

X

1

X

11

0

X

0

0

10

X

X

X

X

13

𝐾3 = ̅̅̅̅

𝑄4

Q2 Q1

J4

Q4Q3

00

01

11

10

00

1

0

0

X

01

X

0

X

X

11

X

X

X

X

10

X

X

X

X

Q2 Q1

K4

Q4Q3

Bảng 2-8: Karnough J4

̅̅̅1

𝐽4 = 𝑄

Bảng 2-9: Karnough K4

00

01

11

10

00

X

X

X

X

01

X

X

X

X

11

0

X

1

0

10

0

X

X

X

K4 = Q 1

Vậy với 4bit thì mạch đếm vịng dùng JK-FF có các phương trình kích sau:

𝐽1 = 𝑄2

𝐽3 = 𝑄4

̅̅̅2

𝐾1 = 𝑄

̅̅̅4

𝐾3 = 𝑄

𝐽2 = 𝑄3

̅̅̅1

𝐽4 = 𝑄

̅̅̅3

𝐾2 = 𝑄

𝐾4 = 𝑄1

J4

K4

Q4 J3

Q3

Q2

J2

J1

Q1

JK-FF

JK-FF

JK-FF

JK-FF

̅̅̅

1

̅̅̅

3

4

̅̅̅1

2

̅̅̅

𝑄2 K1

𝑄3 K2

𝑄

𝑄4 K3

Hình 2.6: Sơ đồ logic 4 bit

Sau khi tìm kiếm được mạch vịng sử dụng JK-FF với số bit rút gọn là 4 và vẽ

được sơ đồ logic ta có thể tìm kiếm được sơ đồ logic của mạch vòng dùng JK-FF với số

bit là 10.

14

+ Lập bảng chuyển đổi trạng thái và giá trị các đầu vào kích 10bit xếp theo mã

johnson

S

S0

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

S14

Q10 Q9

0 0

1 0

1 1

1 1

1 1

1 1

1 1

1 1

1 1

1 1

1 1

0 1

0 0

0 0

0 0

0 0

0 0

0 0

0 0

0 0

S15

S16

S17

S18

S19

Q8

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

Q7

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

Q6

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

Q5

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

Q4

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

Q3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

Q2

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

Q1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

Q`10 Q`9 Q`8

1 0 0

1 1 0

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

1 1 1

0 1 1

0 0 1

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

0 0 0

Q`7

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

Q`6

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

Q`5

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

Q`4

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

Q`3 Q`2

0 0

0 0

0 0

0 0

0 0

0 0

0 0

1 0

1 1

1 1

1 1

1 1

1 1

1 1

1 1

1 1

1 1

0 1

0 0

0 0

Bảng 2-10: Bảng chuyển đổi trạng thái 10 bit

J10 K10 J9 K9 J8 K8

J7 K7

J6 K6

J5 K5

J4 K4

J3 K3

J2 K2

J1 K1

1 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

X

0

1 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

X 0

X 0

1 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

X

0

X 0

X 0

1 X

0 X

0 X

0 X

0 X

0 X

0 X

X

0

X 0

X 0

X 0

1 X

0 X

0 X

0 X

0 X

0 X

X

0

X 0

X 0

X 0

X 0

1 X

0 X

0 X

0 X

0 X

X

0

X 0

X 0

X 0

X 0

X 0

1 X

0 X

0 X

0 X

X

0

X 0

X 0

X 0

X 0

X 0

X 0

1 X

0 X

0 X

15

Q`1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

X

0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

1 X

0 X

X

0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

1 X

X

1

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X

0

X

1 X 0

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X

0

0 X

X

X 0

X 0

X 0

X 0

X 0

X 0

X 0

X

0

0 X

0 X

X

X 0

X 0

X 0

X 0

X 0

X 0

X

0

0 X

0 X

0 X

X

X 0

X 0

X 0

X 0

X 0

X

0

0 X

0 X

0 X

0 X

X

X 0

X 0

X 0

X 0

X

0

0 X

0 X

0 X

0 X

0 X

X

X 0

X 0

X 0

X

0

0 X

0 X

0 X

0 X

0 X

0 X

X

X 0

X 0

X

0

0 X

0 X

0 X

0 X

0 X

0 X

0 X

X

X 0

X

0

0 X

0 X

0 X

0 X

0 X

0 X

0 X

0 X

1

1

1

1

1

1

1

X

1

Bảng 2-11: Bảng giá trị các đầu vào kích 10 bit

+ Xác định phương trình đầu vào kích: Từ bảng chuyển đổi trạng thái, tối thiểu

hóa cho các đầu vào kích ta có hệ phương trình kích:

- 𝐽1 = 𝑄2

̅̅̅̅

- 𝐾3 = 𝑄

4

- 𝐽6 = 𝑄7

̅̅̅̅

- 𝐾8 = 𝑄

9

̅̅̅̅

- 𝐾1 = 𝑄

2

̅̅̅̅

- 𝐽4 = 𝑄

1

̅̅̅̅

- 𝐾6 = 𝑄

7

- 𝐽9 = 𝑄10

- 𝐽2 = 𝑄3

- 𝐾4 = 𝑄1

- 𝐽7 = 𝑄8

̅̅̅̅̅

- 𝐾9 = 𝑄

10

̅̅̅̅

- 𝐾2 = 𝑄

3

- 𝐽5 = 𝑄6

̅̅̅̅

- 𝐾7 = 𝑄

8

̅̅̅̅

- 𝐽10 = 𝑄

1

- 𝐽3 = 𝑄4

̅̅̅̅

- 𝐾5 = 𝑄

6

- 𝐽8 = 𝑄9

- 𝐾10 = 𝑄1

16

𝐽5

𝐾5

𝐽10

𝐾10

𝑄5 𝐽4

𝑄4

JK

JK

FF 𝑄

̅̅̅4

̅̅̅5 𝐾4 FF 𝑄

5

4

𝐽

𝑄

JK 𝑄10 9 JK 9

FF ̅̅̅̅̅

FF

̅̅̅9

𝑄10 𝐾9

𝑄

10

9

𝐽3

𝐾3

𝐽8

𝐾8

𝑄

𝑄1

𝐽1

𝐽2

JK 𝑄3

JK

JK 2

FF 𝑄

̅̅̅2 𝐾 FF 𝑄

̅̅̅3 𝐾2 FF 𝑄

̅̅̅1

1

3

1

2

𝑄

JK 8

FF 𝑄

̅̅̅8

8

𝐽7

𝐾7

JK

FF

7

𝑄7

̅̅̅7 𝐾6

𝑄

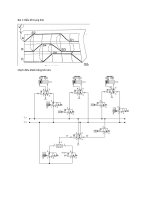

Hình 2.7: Sơ đồ logic mạch 10 bit

2.3

Mơ phỏng

Hình 2.8: Mạch mơ phỏng trên Proteus

17

𝐽6

JK

FF

6

𝑄6

̅̅̅6

𝑄

Thiết kế sơ đồ nguyên lý

2.4

Nhóm chúng em thiết kế mạch trên phần mềm Altium Designer

Hình 2.9: Sơ đồ mạch ngun lý

2.4.1 Các linh kiện chính trong mạch

STT

Tên linh

Số

kiện

lượng

Thơng số kỹ thuật

Chức

năng

Nguồn điện áp đầu vào 2 – 18V

1

IC LM555

1

Dòng điện tiêu thụ: 6 – 15mA

Tạo xung

Điện áp logic đầu ra ở mức cao: 0.5 – 15V

cho mạch

Điện áp logic đầu ra ở mức thấp: 0.03 – điều khiển

0.06V

IC gói JK Flip Flop kép

2

IC74LS73

5

Điện áp hoạt động: 5V

Điều khiển

Điện áp đầu vào mức cao: 2 V

các led

Điện áp đầu vào mức thấp: 0,8 V

Điện áp đầu vào 3V

3

LED

11

Hiển thị

Màu sắc: Vàng

Đường kính: 5mm

18

4

5

6

6

Biến trở

Điện trở

Điện trở

Tụ điện

1

13

3

1

Sai số: 10%

Điều chỉnh

Công suất: 2W

tốc độ nháy

Giá trị: 10K

của led

Loại 4 vòng màu

Bảo vệ

Sai số 5%

linh kiện

Giá trị 1K

trong mạch

Loại 4 vòng màu

Thiết kế

Sai số 5%

mạch tạo

Giá trị 10K

xung

Điện dung: 100uF

Thiết kế

Điện áp: 50V

mạch tạo

Nhiệt độ hoạt động: -55°C — 125°C

xung

Loại bóng bán dẫn: NPN

7

Transistor

C1815

11

Dịng điện tối đa: 150mA

Điều khiển

Điện áp cực đại: 50V

LED

Điện áp cực đại cực phát (VEBO): 5V

8

Nút nhấn

1

Số chấn của nút nhấn 4 chân

Reset

Kích thước: 6x6x4.3MM

mạch

Bảng 2-12: Bảng linh kiện sử dụng trong mạch

2.4.2 Khối tạo xung - IC555

Hình 2.10: Khối tạo xung – IC555

19