Hệ thống điều khiển chuông lớp học P2 ppsx

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (535.68 KB, 12 trang )

6. Khối giải mã đổ chuông

Khối giải mã đổ chuông là khối tương đối phức tạp trong đề tài này, bởi dữ

liệu cần giải mã là 24bit – là tổng số bit đầu ra của các IC đếm, với số bit lớn như

vậy trong thực tế người ta hay dùng Vi điều khiển họ 8051, hoặc PIC để giải mã

tuy nhiên do yêu cầu của môn học là “Đề tài thiết kế mạch tương tự” nên yêu cầu

đượ

c đặt ra là thiết kế mạch dùng các phần tử logic và các IC số cơ bản. Do đó

mạch không tránh khỏi sự cồng kềnh.

Qua tìm hiểu chúng em thấy Khoa Công Nghệ Điện Tử-Thông Tin, trường

Viện Đại Học Mở Hà Nội tổ chức 3 buổi học là: buổi sáng, buổi chiều và buổi tối,

mỗi buổi học có 4 tiết học, ở giữa các tiết học có 10 phút ra chơi, riêng giờ ra chơi

sau tiết thứ 3 là 15 phút đã được trình bày ở mục Phân tích bài toán.

Do các ca học là giống nhau và cũng do mức độ phức tạp của đề tài nên

chúng em chỉ thiết kế mạch giải mã đổ chuông cho một buổi học. Giả sử ta thiết

kế bộ giải mã đổ chuông cho ca học buổi sáng:

Thời gian đổ chuông của ca học này như sau:

Tiết học Bắt đầu kết thúc Nghỉ

1 7h15 8h15 10'

2 8h25 9h25 10'

3 9h35 10h05 15'

4 10h20 11h15 0’

Để thiết kế mạch giải mã này ta cần phải lập một hàm y = f(x

0

, x

2

,…x

23

)

Khi đó tại các thời điểm có đổ chuông y sẽ có giá trị 1.

Chúng ta xây dựng mạch giải mã dựa trên phần tử logic AND để nhận biết các mốc

thời gian tức là nhận biết các số thập phân từ 0 đến 9.

giải sử tại thời điểm là 07 giờ 15 phút 00 giây ta dùng mạch AND để nhận biết các

số 0 và 7 như sau:

Mạch giải mã 0:

U1A

U2D

U2C

U2B

U2A

Mạch giải mã 7:

Sau khi nhận biết được các giá trị thập phân của bộ đếm thời gian ta tiến hành

kết hợp các giá trị ở đầu ra các mạch AND để được mạch giải mã tại thời điểm 7

giờ 15’, các thời điểm khác cũng tiến hành tương tự như trên.

Sau khi đã giải mã hết các thời điểm để đổ chuông ta tiế

n hành xây dựng mạch

phân biệt đâu là thời điểm đổ chuông ra chơi, đâu là thời điểm đổ chuông vào học

bằng mạch OR như sau:

Ta thấy để thực hiện mạch này ta phải sử dụng rất nhiều mạch AND có 4, 6 cổng

vào, bên cạnh đó phải phối hợp với các cổng NOT rất cồng kềnh và khó thực hiện.

Trên thực tế để thiết kế mạch này ta dùng phương pháp đơn giản hơn đó là: Ta tiến

hành giải mã từ mã BCD của bộ đếm sang mã thập phân sử dụng IC 74HC4028

sau đó tiến hành chọn các thời điểm đổ chuông bằng mạch AND 6 cổng vào. Do

thời gian báo chuông vào học là 5s, báo chuông ra chơi là 10s cho nên ta sử dụng

mạch OR 5 cổng để tổng hợp các tín hiệu ra của các mạch AND thành 2 tín hiệu

đổ chuông ứng với chuông vào học và chuông ra ch

ơi.

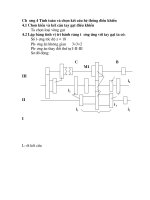

Bộ giải mã khi thiết kế:

7. Khối chuông :

- Khối chuông bao gồm hệ thông kích chuông và chuông, chuông có thể là chuông

điện tử hoặc chuông cơ học, nếu là chuông điện tử công suất nhỏ chỉ cần nối trực

tiếp với đầu ra của FET.

- Hệ thông kích chuông bao gồm 1 transistor trường làm việc như một khoá điện tử

đế đóng mở dòng điện điều khiển chuông. Khi có xung dương kích thích từ bộ giải

mã đến đầu vào của bộ kích chuông, một tụ điện được nối song song với cực

Source và Gate của Transistor trường được nạp điện để duy trì điện áp giữa cực S

và D của FET. Thời gian mở của FET phụ

thuộc vào giá trị của tụ điện và điện trở

mắc song song với nó.

- Thời gian mở của FET được tính gần bằng: t = 0.8xCxR

- Đối với mạch trẽ 5s ta có: t=0,8x47x10

6

x120x10

3

=5a

- Đối với mạch trễ 10s ta có: t=0,8x100x10

6

x120x10

3

=10s

Do thời gian đổ chuông lúc ra chơi và vào học là khác nhau nên ta sử dụng 2 mạch

khoá kiểu này và nối vào các đầu ra của bộ giải mã đổ chuông.

-Sơ đồ khối kích chuông:

Nếu dùng các loại chuông cơ học có công suất lớn, khi đó đầu ra của FET sẽ được

nối với môt rơle để điều khiển loại chuông đó như hình sau:

VI. Sơ đồ mạch của hệ thống

Dùng phần mềm vẽ mạch Orcad trên máy tính sẽ cho ta sơ đồ mạch của hệ thống

như sau :

SƠ ĐỒ MẠCH HỆ THỐNG ĐIỀU KHIỂN CHUÔNG LỚP HỌC

VII. Một số linh kiện được dùng trong hệ thống

1. IC giải mã 7 đoạn 74LS47

Vi mạch giải mã 7 đoạn 74LS47 là loại IC có 16 chân dùng để giải mã từ mã BCD

sang mã 7 đoạn để hiển thị được trên led 7 đoạn.

- Hình dạng và sơ đồ chân trong thực tế:

- Chức năng của các chân IC 74LS47 như sau:

+ Chân số 8 là chân nối đất (0V)

+ Chân số 16 là chân nguồn cung cấp

+ Chân 1,2,6,7 là các chân tín hiệu vào BCD

+ Chân 9,10,11,12,13,14,15 là các chân đầu ra.

+ Chân 3,4,5 là các chân kiểm tra IC

- Bảng chân lý của IC 74LS47:

- Sơ đồ logic:

2. IC đếm mode 10 74HC192

74HC192 là vi mạch đếm mod 10 thông dụng được sử dụng rất nhiều trong

thực tế, bới nó được chế tạo trên công nghệ tiết kiệm điện năng, nó có thể đếm

tiến, đếm lùi, đếm có dữ liệu vào và có chức năng reset…

- Hình dạng và sơ đồ chân trong thực tế:

- Mô tả các chân của IC 74HC192:

Thứ tự chân Kí hiệu Tên và chức nă

ng

3, 2, 6, 7

4

5

8

11

12

13

14

15, 1, 10, 9

16

Q

0

đến Q

3

CP

D

CP

U

GND

PL

TC

U

TC

D

MR

D

0

đến D

4

V

CC

Đầu ra BCD của bộ đếm

Lối vào của xung đến lùi

Lối vào của xung đến tiến

Nối đất (0V)

Tải dữ liệu song song (Active LOW)

Lối ra cờ mang (Active LOW)

Lối ra cờ muợn (Active LOW)

Reset (Active HIGH)

Dữ liệu vào bộ đếm

Nguồn cung cấp

- Bảng chế độ hoạt động:

Sơ đồ logic :

3. IC giải mã BCD sang mã 10 74HC4028

Vi mạch 74HC4028 là loại vi mạch giải mã thông dụng 16 chân chuyên dùng để

giải mã tín hiệu BCD sang mã 10, loại IC này sử dụng công nghệ CMOS để chế

tạo nên tốc độ hoạt động rất cao tiết kiệm điện năng.

-Sơ đồ chân trong thực tế:

- Chức năng của các chân vi mạch 74HC4028 như sau:

+ Chân số 1,2,3,4,5,6,7,9,14,15 là các chân đâu ra dữ liệu thập phân tương ứng với

các chân Y4,Y2,Y0,Y7,Y9,Y5,Y6,Y8,Y1,Y3.

+ Chân số 10,11,12,13 là các chân dữ liệu đầu vào BCD tương ứng với các chân

A, D, C, B

+ Chân số 8 là chân nối đất (0v)

+ Chân sô 16 là chân cấp nguồn.

- Bảng chân lý của IC 74HC4028

- Sơ đồ logic:

4. IC tích hợp phần tử OR 74LS32P

IC 74LS32P là loại IC tích hợp phần tử OR, trong 1 IC chứa 4 phần tử OR, các

chân của nó được trình bày như hình vẽ, chân số 7 nối đất, chân 14 là chân nguồn.

5. IC tích hợp phần tử AND 74LS08

IC 74LS08 là loại IC tích hợp phần tử AND, trong 1 IC chứa 4 phần tử

AND, các chân của nó được trình bày như hình vẽ, chân số 7 nối đất, chân 14 là

chân nguồn.

6. Led 7 đoạn

Led 7 đoạn là một linh kiện hiển thị mã 7 đoạn chuyên dụng, nó hiển thị 16 giá trị

tương ứng với mã BCD

Led 7 đoạn có 2 loại: loại chung anot và loại chung catot.

Led 7 đoạn cũng có rất nhiều màu sắc khác nhau.

Trong đề tài này có sử dụng 6 led 7 đoạn chung anot để hiển thị thời gian.

Hình dạng và sơ đồ của led 7 đoạn trong thực tế: