Giáo trình cơ điện: Thiết kế,lập trình và điều chỉnh cho việc tự động hóa trong nông nghiệp phần 9 potx

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (895.13 KB, 10 trang )

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 73 -

nguyên phần cứng nào của thiết bị PSoC. Bộ nhớ Flash của thiết bị PSoC đợc

tổ chức dới dạng 256 khối 64 byte đối với thiết bị 16 K. Kỹ thuật Flash của

PSoC cho phép đọc từng byte dữ liệu trong bộ nhớ Flash, nhng khi viết lại thì

yêu cầu phải viết cả 64 byte cùng một lúc. Vùng lu trữ của E2PROM phải

bắt đầu tại đờng biên khối bộ nhớ Flash và có thể bao gồm 1 hoặc nhiều

byte. Sử dụng các hàm API là E2Read() và E2Write() để đọc và ghi dữ liệu.

Hàm E2Read() của API đọc bộ nhớ Flash bằng cách sử dụng lệnh ROMX của

M8C. Lệnh này cho phép đọc bộ nhớ Flash theo từng byte một cách có hiệu

quả. Nó yêu cầu sử dụng 8 byte cuối cùng của RAM, từ 0xF8 0xFF. Hàm

E2Write() của API ghi dữ liệu của bộ nhớ Flash theo từng khối, dựa trên địa

chỉ đầu của không gian nhớ E2PROM, hàm E2Write() phân tích dữ liệu đợc

viết thành nhiều phần và dựa theo đờng biên của từng khối, nó cũng yêu cầu

sử dụng 8 byte cuối cùng của RAM từ 0xF8 0xFF.

3.4. Phần mềm phát triển PSoC Designer 4.2

PSoC Designer là phần mềm phát triển hỗ trợ ngời thiết kế trong việc

cấu hình phần cứng và lập trình phần mềm cho các chip PSoC trên máy PC

thông thờng và sau đó nạp vào chip qua Kit ICE. Do điều kiện làm đồ án

này không có Kit ICE cho nên tôi dùng bộ MiniDevelopment Kit để nạp

chơng trình vào chip.

Mọi hỗ trợ kỹ thuật và phần mềm miễn phí đợc cung cấp trên trang

chũ của hãng sản xuất Cypress: /> và

/> .

3.4.1. Cấu trúc của PSoC Designer

Phần mềm PSoC Designer đợc chia làm 3 phần chính:

* Device Editor - Trình soạn thảo cấu hình chip.

* Application Editor - Trình soạn thảo ứng dụng.

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 74 -

* Debugger - Trình gỡ rối.

3.4.2. Các kiểu file và đuôi mở rộng

Khi bạn tạo một dự án thì một th mục gốc với 3 th mục con sẽ đợc

tạo ra tại vị trí mà bạn định trớc. Tên của th mục gốc lấy theo tên của dự án,

tên của 3 th mục con là lib(Librarian), obj(Objects), output(chứa file nạp

xuống chip).

3.4.3. Tạo một dự án trong PSoC Deisigner

a. Tạo một dự án hoàn toàn mới.

Ban đầu để chạy PSoC Designer thì chỉ việc kích đúp vào biểu tợng

PSoC Designer.exe. Khi đó để cấu hình cho chip những chức năng mong muốn

thì trớc hết ta phải tạo một th mục cho dự án để chứa các tệp của dự án.

3. Sau khi chạy chơng trình sẽ xuất hiện cửa sổ Start, khi đó ta kích

vào nút Start New Project để tạo ra một dự án mới.

Hình 3-15: Cửa sổ khởi động chơng trình

3. Khi đã nhấn vào nút Start New Project thì trên màn hình xuất hiện

cửa sổ New Project. Khi đó ta chỉ việc đánh tên của dự án vào phần New

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 75 -

Project name và định vị cho dự án tại mục New Project location bằng cách gõ

đờng truyền hoặc nhấn nút Browse.

Hình 3-15: Cửa sổ khởi tạo chơng trình mới

3. Khi thực hiện xong thì nhấn vào nút Next. Khi đó sẽ xuất hiện hộp

thoại Creat New Project. Trong phần Family ta chọn họ chip, trong phần Part

ta chọn loại chip thích hợp trong họ chip đó. Trong phần Generate Main file

using ta chọn ngô ngữ lập trình là C hay Assembly.

3. Sau khi hoàn tất thì nhấn nút Finish để kết thúc khi đó ta đã tạo ra

một dự án hoàn toàn mới.

b. Tạo một dự án dựa trên những thiết kế có sẵn

Ta có thể tạo ra một dự án mới dựa trên những thiết kế đã đợc xuất

thành file. Một cấu hình có thể nạp lại bao gồm một hay nhiều User Module

đã đợc sử dụng với những thông số xác định. Tính năng này giúp bạn sử

dụng lại những tham số của cấu hình trớc hiệu quả và tiết kiệm thời gian. Khi

đó bạn tiến hành các bớc sau:

3. Bắt đầu bạn tiến hành nh khi tạo ra một dự án hoàn toàn mới nhng

trong hộp thoại New Project bạn chọn Designe - Based Project trong phần

Select Method. Nhập tên cho dự án và định vị nơi lugiữ dự án.

3. Chọn Next khi đó sẽ xuất hiện hộp thoại hỏi bạn là có muốn tạo th

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 76 -

mục mới cho dự án với tên mới hay không? chọn Yes.

3. Trong hộp thoại Designed Based Project chọn Designed Brows để

link đến dự án đã có sẵn mà ta muốn sao chép lại ở dự án mới này. Khi đó bạn

cũng có thể thay đổi đợc họ chip điều khiển và ngôn ngữ lập trình bằng cách

vào phần Select Base Part.

Hình 3-16: Cửa sổ khởi tạo chơng trình theo thiết kế đã có sẵn

3. Sau đó thì nhấn nút finish để hoàn tất công việc và khi đó bạn đã tạo

ra một dự án mới dựa trên một thiết kế đã có sẵn.

3.4.4. Trình soạn thảo cấu hình chip - Device Editor

1. Lựa chọn User Module

Lựa chọn User Module cho ứng dụng của bạn là bớc đầu tiên cần phải

làm để cấu hình cho chip. Một User Module là một chức năng đợc cấu hình

trớc và nó sẽ làm nh là một ngoại vi trên chip.

Để truy nhập vào Device Editor, nhấn nút

khi đó PSoC Designed sẽ

mở chế độ lựa chọn User Module. Khi đó tuỳ thuộc vào chức năng của từng

Module và yêu cầu bài toán điều khiển của bạn mà bạn gọi các Module ra

bằng cách nhấn đúp vào Module cần lựa chọn.

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 77 -

Hình 3-17: Cửa sổ thiết lập phần cứng chơng trình

Sau khi đã lựa chọn những User Module cần thiết ta chuyển sang chế độ

Interconnection View bằng cách nhấn nút

.

2. Cách đặt một User Module

Khi muốn sử dụng một User Module thì ta phải đặt nó vào trong các

khối tài nguyên của chip bằng cách:

ế. Click đơn vào User Module đợc lựa chọn, khi đó Module đợc chọn

sẽ có một khối chức năng(hoặc hai khối tuỳ thuộc vào cấu hình của Module

đó) sáng lên.

ế Ta nhấn vào nút Next Allowed Placement để chuyển khung sáng

sang vị trí hợp lý cuối cùng bạn nhấn nút

để định vị tại khối chức năng của

Module.

ế Nếu muốn gỡ bỏ User Module nào thì chỉ cần chọn User Module đó

nhấn chuột phải và chọn vào nút Unplace. Một số User Module không sử

dụng đến khối tài nguyên nh LCD, I2C vì vậy không cần định vị.

3. Chọn thông số cho chip

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 78 -

Khi thiết lập thông số cho chip ta phải căn cứ vào tính năng của chip mà

bạn đang dùng và yêu cầu điều khiển mà điền thông số vào cột Value của

Global Resource

Hình 3-18: Cửa sổ kết nối chân và thông số cho chip.

4. Kết nối các User Module

Việc kết nối các User Module đợc thực hiện thông qua các đầu vào ra

của các khối chức năng nắm giữ các User Module và thông qua một đờng

bus chung.

5. Xuất thiết kế thành file

Khi cấu hình xong ta tiến hành xuất thiết kế thành file bằng cách:

- Chọn Menu Config>>Export Design.

- Trong trờng Designed Name điền tên của file định xuất ra.

- Trong trờng Description điền thông tin miêu tả về thiết kế.

- Trong trờng Version điền phiên bản của thiết kế.

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 79 -

Sau đó nhấn OK là bạn đã hoàn tất việc cấu hình chip.

3.4.5. Trình soạn thảo ứng dụng - Application Editor

Để vào trình soạn thảo(Viết code gọi lệnh điều khiển các khối chức năng)

ta nhấn nút

. Sau đó bạn nhấn vào Source files kích đúp vào main.c để viết

lệnh sau dòng // Insert your main routine code here.

Hình 3-19: Cửa sổ lập chơng trình

Sau khi viết code xong ta nhấn F7 để dịch chơng trình. Nếu không có lỗi

thì ta tiến hành dịch chơng trình sang file.hex để phục vụ cho việc nạp chip.

Ta vào menu Program>>Write Hex file. Sau đó đặt tên file, định vị file và

nhấn OK là ta đã có file.hex.

3.5. Bộ điều khiển PID số

3.5.1. Thiết kế luật điều khiển PID số

1. Luật điều khiển tỷ lệ : Proportional (P)

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 80 -

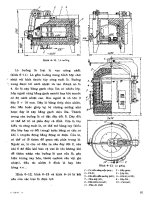

Hình 3 - 20 : Hệ kín với luật điều khiển tỷ lệ

r(t): Tín hiệu đầu vào của hệ thống.

y(t): Tín hiệu đầu ra của hệ thống.

u(t): Tín hiệu điều khiển tác động lên đối tợng.

e(t): Tín hiệu sai lệch điều khiển.

Khi đó sai lệch e(t) = r(t) - y(t) là đầu vào của bộ điều khiển và u(t) là đầu

ra của bộ điều khiển thì quan hệ giữa đầu vào và đầu ra của luật điều khiển

đợc biểu diễn theo phơng trình sau.

u(t) = k

P

.e(t) (3 - 1)

Trong đó K

P

là tham số của luật điều khiển. Hỗn hợp các đối tợng công

nghiệp đều đợc điều khiển theo luật này. Bởi luật điều khiển tơng đối đơn

giản nhng lại có thể thay đổi cả chất lợng động và chất lợng tĩnh của hệ

thống. Khi ta thay đổi giá trị k

P

dẫn đến sự thay đổi hệ số khuyếch đại của hệ

hở, điều đó dẫn đến sự thay đổi vị trí của điểm cực và điểm không của hệ. Khi

k

P

thay đổi cũng làm chất lợng của hệ thống ở chế độ xác lập thay đổi:

=)(t

lim

t

s.E(s) =

lim

t

)(.1

)(.

swK

sRs

dtP

+

(3 - 2)

1. Luật điều khiển tích phân: Integral(I)

u(t)

Kp

e(t)

r(t)

_

Đối tợng

điều khiển

y(t)

u(t)

9

u(t)

sT

I

.

1

e(t)

r(t)

_

Đối tợng

điều khiển

y(t)

u(t)

9

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 81 -

Hình 3 - 21: Hệ kín với luật điều khiển tích phân

Với tín hệu đầu vào của bộ điều khiển là sai lệch e(t) và tín hiệu đầu ra

u(t) ta có thể biểu diễn luật điều khiển tích phân bằng phơng trình sau:

u(t) =

t

I

de

T

0

).(

1

(3 - 3)

hoặc u(t) = k

I

t

de

0

).(

(3 - 4)

Tham số của luật điều khiển là T

I

đợc gọi là hằng số thời gian tích

phân hay K

I

là hệ số tích phân. Khi sử dụng luật điều khiển tích phân độ dự

trữ ổn định của hệ kín sẽ giảm đi, theo tiêu chuẩn ổn định của Nyquist sai

lệch tĩnh sẽ giảm vì hàm truyền của hệ hở lúc đó là:

w

0

= w

DK

(s) - w

dt

=

sT

I

1

w

dt

(s) (3 - 5)

và sai lệch của hệ là:

=)(t

lim

t

)(

1

1

)(.

swsT

sRs

dtI

+

=

lim

t

)(

).(.

2

swT

ssRT

dtI

I

+

(3 - 6)

Điều khiển tích phân hay còn gọi là phơng pháp điều khiển theo tích

luỹ sai lệch điều khiển chậm sau. Phơng pháp điều khiển này có u điểm

là ít chịu ảnh hởng của nhiễu và làm tăng độ chính xác của hệ hở ở chế độ

xác lập.

3. Luật điều khiển vi phân : Derivative(D)

Hình 3 - 22:Hệ kín với luật điều khiển vi phân

Luật vi phân đợc biểu diễn theo phơng trình sau:

u(t)

T

D

S

e(t)

r(t)

_

Đối tợng

điều khiển

y(t)

u(t)

9

.

Đồ án tốt nghiệp Nguyễn Thái Học - Lớp TĐH 46

Khoa Cơ Điện Trờng ĐHNN I - H Nội

- 82 -

u(t) = T

D

dt

tde

)(

(3 - 7)

Trong đó T

D

là hằng số thời gian vi phân. Luật điều khiển vi phân có

tác dụng làm giảm thời gian quá độ của hệ. Do đó ngời ta gọi đây là luật

điều khiển vợt trớc. Quyết định điều khiển đợc đa ra trên cơ sở đạo

hàm của sai lệch. Nhợc điểm của luật này là ở phơng pháp lấy thông tin

này vì nếu đối tợng chịu ảnh hởng của nhiễu biến thiên thì luật sẽ ra

quyết định theo nhiễu do đó luật điều khiển với các đối tợng có nhiễu là

hằng số hoặc ít bị nhiễu.

4. Luật điều khiển PID

Đây là bộ điều khiển tích hợp của ba luật điều khiển trên vì thế nó sẽ

tích luỹ đợc tất cả điểm mạnh của các luật trên và khắc phục những hạn chế

của từng luật cụ thể.

Thành phần khuyếch đại (P) có tốc xử lý tín hiệu nhanh, có độ ổn

định cao, thời gian điều khiển ngắn. Nhng hạn chế của quy luật này

là khi hệ thống ở trạng thái xác lập luôn tồn tại sai lệch tĩnh.

Thành phần tích phân (I) có u điểm là triệt tiêu đợc sai lệch tĩnh

nhng tốc độ xử lý tín hiệu còn chậm.

Thành phần vi phân (D) có tác dụng làm tăng nhanh tốc độ tác động

của tín hiệu điều khiển nhng bên cạnh đó luật điều khiển này có độ

quá điều chỉnh lớn.

Sơ đồ cấu trúc của luật điều khiển:

.