THIẾT kế lõi IP CHO MẠNG nơ RON CÔNG NGHỆ 0 5 UM

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (2.26 MB, 71 trang )

ĐỒ ÁN TỐT NGHIỆP

THIẾT KẾ LÕI IP CHO MẠNG NƠ RON

CÔNG NGHỆ 0.5 UM

1

MỤC LỤC

DANH MỤC CÁC HÌNH VẼ.........................................................................................VIII

DANH MỤC CÁC TỪ VIẾT TẮT...................................................................................XI

CHƯƠNG 1. GIỚI THIỆU ĐỀ TÀI...................................................................................1

1.1

GIỚI THIỆU..............................................................................................................1

1.2

MỤC TIÊU................................................................................................................1

1.3

NỘI DUNG................................................................................................................1

CHƯƠNG 2. TỔNG QUAN VỀ THIẾT KẾ CHIP CMOS............................................2

2.1

GIỚI THIỆU VỀ THIẾT KẾ CHIP CMOS...............................................................2

2.1.1

Lý thuyết thiết kế chip.........................................................................................2

2.1.2

Công nghệ CMOS...............................................................................................2

2.1.3

Ngôn ngữ thiết kế VHDL.....................................................................................4

2.1.4

Công cụ thiết kế Alliance....................................................................................5

2.2

KỸ THUẬT THIẾT KẾ CHIP CMOS......................................................................7

CHƯƠNG 3. THIẾT KẾ LÕI IP CHO MẠNG NƠ RON............................................10

3.1

TỔNG QUAN VỀ MẠNG NƠ RON NHÂN TẠO................................................10

3.2

CẤU TRÚC TỔNG QUAN CỦA MỘT MẠNG NƠ RON....................................10

3.3

QUÁ TRÌNH XỬ LÝ THÔNG TIN CỦA MỘT MẠNG NƠ RON........................11

3.4

HUẤN LUYỆN MẠNG NƠ RƠN..........................................................................12

3.5

SƠ ĐỒ KHỐI MẠNG NƠ RON.............................................................................13

3.6

QUY TRÌNH THIẾT KẾ CHIP CHO MẠNG NƠ RON........................................15

CHƯƠNG 4. KẾT QUẢ THU ĐƯỢC..............................................................................18

4.1

KẾT QUẢ THIẾT KẾ LUẬN LÝ...........................................................................18

4.1.1

Mô phỏng dạng sóng.........................................................................................18

4.1.2

Kết quả thu được trên KIT................................................................................21

4.1.3

Thiết kế mạch....................................................................................................24

4.2

KẾT QUẢ THIẾT KẾ VẬT LÝ..............................................................................27

2

4.2.1

Thiết kế layout...................................................................................................27

4.2.2

Kiểm tra LVS và DRC.......................................................................................31

CHƯƠNG 5. KẾT LUẬN..................................................................................................33

5.1

KẾT LUẬN..............................................................................................................33

5.1.1

Ưu điểm.............................................................................................................33

5.1.2

Nhược điểm.......................................................................................................33

5.1.3

Kết quả đạt được...............................................................................................33

5.2

HƯỚNG PHÁT TRIỂN...........................................................................................33

TÀI LIỆU THAM KHẢO..................................................................................................34

PHỤ LỤC A ........................................................................................................................35

3

DANH MỤC CÁC HÌNH VẼ

HÌNH 2-1: CẤU TẠO CỦA MỘT CỔNG CMOS [3]......................................................3

HÌNH 2-2: CÁC CÔNG CỤ LIÊN KẾT VỚI NHAU TRÊN ALLIANCE...................7

HÌNH 2-3: QUY TRÌNH THIẾT KẾ LUẬN LÝ VÀ THIẾT KẾ VẬT LÝ..................9

HÌNH 3-1: CẤU TRÚC TỔNG QUÁT CỦA MỘT MẠNG NƠ RON [4]...................10

HÌNH 3-2: QUÁ TRINH XỬ LÝ THÔNG TIN CỦA MỘT MẠNG NƠ RON [4]....11

HÌNH 3-3: SƠ ĐỒ KHỐI MẠNG NƠ RON....................................................................13

HÌNH 3-4: MÔ TẢ TÍN HIỆU NÃO NGƯỜI [4]...........................................................14

HÌNH 3-5: MÔ TẢ TÍN HIỆU ĐƯỢC KHỐI ALPHA XỬ LÝ [4]..............................14

HÌNH 3-6: QUY TRÌNH THIẾT KẾ CHIP CHO MẠNG NƠ RON...........................15

HÌNH 4-1: MÔ PHỎNG TRÊN MODELSIM................................................................18

HÌNH 4-2: CÔNG SUẤT CỦA THIẾT KẾ.....................................................................19

HÌNH 4-3: TỔNG HỢP RTL CỦA KHỐI TIMER........................................................20

HÌNH 4-4: KẾT QUẢ THỰC THI CODE TRÊN KIT VỚI INPUT 1 VÀ 2..............21

HÌNH 4-5: KẾT QUẢ THỰC THI CODE TRÊN KIT VỚI INPUT 3........................22

HÌNH 4-6: KẾT QUẢ THỰC THI CODE TRÊN KIT VỚI INPUT 2........................23

HÌNH 4-7: MẠCH SCHEMATIC CỦA NƠ RON..........................................................24

HÌNH 4-8: PHÓNG LỚN 1 KHỐI TRONG MẠCH NƠ RON....................................25

HÌNH 4-9: KẾT QUẢ QUÁ TRÌNH TỔNG HỢP MẠCH TỪ CODE........................26

HÌNH 4-10: THIẾT KẾ LAYOUT CỦA KHỐI NƠ RON............................................27

HÌNH 4-11: PHÓNG TO MỘT PHẦN THIẾT KẾ LAYOUT......................................28

HÌNH 4-12: KIỂM TRA LVS CỦA KHỐI NƠ RON.....................................................29

HÌNH 4-13: KIỂM TRA DRC CÔNG NGHỆ 0.5 UM CỦA KHỐI NƠ RON...........30

4

DANH MỤC CÁC BẢNG BIỂU

BẢNG 4-1: THÔNG SỐ LÕI IP CHO MẠNG NƠ RON CÔNG NGHỆ 0.5 UM.....29

BẢNG 4-2: SƠ ĐỒ CHÂN CỦA CON CHIP..................................................................30

5

6

DANH MỤC CÁC TỪ VIẾT TẮT

CMOS

Complementary Metal-Oxide-Semiconductor

VHDL

VHSIC Hardware Description Language

DRC

Design Rule Check

LVS

Layout Versus Schematic

RTL

Register Transfer Lever

7

8

ĐỒ ÁN TỐT NGHIỆP

Trang 1/61

CHƯƠNG 1. GIỚI THIỆU ĐỀ TÀI

1.1 Giới thiệu

Với tốc độ phát triển Khoa học – Kĩ thuật như hiện nay, đặc biệt trong cuộc cách

mạng công nghiệp 4.0 mà thế giới đang phát triển. Trí tuệ nhân tạo đang là vấn đề

nghiên cứu của các công ty công nghệ hàng đầu thế giới được sở hữu bởi các quốc

gia hàng đầu như Mỹ, Đức, Nhật Bản….

Vì vậy việc nghiên cứu mạng nơ ron nói riêng và trí tuệ nhân tạo nói chung đang là

kim chỉ thiên cho các quốc gia muốn phát triển hiện nay.

Việc phát triển mạng nơ ron chủ yếu được thực hiện trên phần mềm hay hệ thống

nhúng. Tuy nhiên việc thực hiện trên phần cứng còn nhiều hạn chế do sự phức tạp

của hệ thống mạng nơ ron. Đây cũng là một hướng nghiên cứu được rất nhiều công

ty công nghệ hướng đến. Đề tài này thực hiện một mạng nơ ron đơn giản trên phần

cứng mô phỏng hoạt động của một mạng nơ ron.

1.2 Mục tiêu

Nắm được quy trình thiết kế chip CMOS cơ bản.

Hiểu được mạng nơ ron là gì và các ứng dụng của mạng nơ ron trong cuộc sống

hiện thực.

Phần nào đó qua đồ án này có thể thiết kế và mô phỏng được một mô hình huấn

luyện mạng nơ ron cơ bản.

1.3 Nội dung

Các nhiệm vụ cần thực hiện ở đồ án này:

Thiết kế được mạng nơ ron với 3 trọng số huấn luyện và 1 sợi thần kinh.

Thiết kế và mô phỏng lõi IP và tổng hợp RTL.

Tổng hợp logic trên Kit. Thiết kế layout và kiểm tra DRC, LVS.

CHƯƠNG 2. TỔNG QUAN VỀ THIẾT

KẾ CHIP CMOS

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 2/61

1.4 Giới thiều về thiết kế chip CMOS

1.1.1 Lý thuyết thiết kế chip

Thiết kế chip là việc tích hợp rất nhiều linh kiện bán dẫn vào một con chip nhỏ để

tạo ra chức năng của con chip. Con chip có thể có 1 hoặc nhiều chức năng tùy vào

nhu cầu của người thiết kế.

Công nghệ thiết kế càng cao, con chip càng được tích hợp nhiều linh kiện và càng

nhỏ gọn. Việc thiết kế muốn đưa vào thực tế phải dựa vào các luật thiết kế.

1.1.2 Công nghệ CMOS

CMOS là thuật ngữ dùng để chỉ một loại công nghệ chế tạo vi mạch tích hợp, viết

tắt của cụm từ “Complementary Metal-Oxide-Semiconductor”. Công nghệ CMOS

được dùng trong chế tạo vi điều khiển, vi xử lý, RAM tĩnh và một số mạch logic

khác. Ngoài ra công nghệ Cmos còn được dùng trong các mạch tương tự như cảm

biến hình ảnh, chuyển đổi dữ liệu và các vi mạch thu phát có mật độ tích hợp cao

trong lĩnh vực thông tin.

Cụm từ “Metal-Oxide-Semiconductor” có nguồn gốc từ một quy trình chế tạo các vi

mạch tích hợp CMOS cũ. Quy trình này tạo ra các transistor hiệu ứng trường mà

mỗi transistor mang một điện cực cổng bằng kim loại được đặt lên trên một lớp

cách điện bằng oxide phủ trên vật liệu bán dẫn.

CMOS có cấu tạo bao gồm cả PMOS và NMOS trong cùng một mạch nên có thể

tận dụng được các thế mạnh của cả 2 loại transistor. Mạch logic được tạo ra từ quy

trình CMOS sẽ tốn ít năng lượng hơn và mật độ tích hợp cao hơn so với các quy

trình khác cùng chức năng.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 3/61

Hình 2-1: Cấu tạo của một cổng CMOS [3]

Một số đặc tính quan trọng của CMOS

Điện áp:

CMOS có thể hoạt động ở mức điện áp từ 3V đến 15V. Tuy nhiên với điện áp nhỏ

hơn 4.5V thời gian trễ sẽ tăng, tính chống nhiễu sẽ bị giảm và tổng trở ra sẽ lớn.

Nhưng với những điện áp lớn hơn 15V cũng sẽ gây ra những bất lợi:

-

Trong lúc CMOS hoạt động công suất tiêu tán sẽ tăng.

-

Những xung nhiễu từ nguồn vượt quá 20V (điện áp đánh thủng) sẽ tạo ra

hiệu ứng SRC-latch_up gây hỏng IC nếu dòng không được hạn chế từ bên

ngoài. Vì vậy với điện áp lớn hơn 15V thì cần phải có điện trở hạn dòng.

Công suất tiêu tán:

Khi mạch CMOS ở trạng thái tĩnh thì công suất tiêu tán của mạch rất nhỏ. Tuy

nhiên khi phải chuyển mạch nhanh thì công suất tiêu tán của CMOS sẽ gia tăng

đáng kể.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 4/61

Tốc độ chuyển mạch:

Với điện áp càng cao thì CMOS hoạt động càng nhanh nhưng kéo theo đó cũng sẽ

làm tăng công suất tiêu tán.

Tính kháng nhiễu:

Thời gian trễ của CMOS có vai giống như một bộ lọc nhiễu. CMOS có tính chống

nhiễu rất tốt lên đến 45% điện áp cấp. Vì tính chống nhiễu tốt, CMOS được dùng để

thiết kế các mạch điện của các thiết bị cộng nghiệp hoạt động trong môi trường đầy

nhiễu điện và điện từ.

1.1.3 Ngôn ngữ thiết kế VHDL

VHDL là ngôn ngữ mô tả phần cứng được sử dụng để mô tả một hệ thống thiết kế

logic. VHDL được phát triển bởi bộ quốc phòng Mỹ. Việc phát triển ngôn ngữ

VHDL nhằm mục tiêu tạo ra một ngôn ngữ phần cứng tiêu chuẩn và thống nhất cho

phép thử nghiệm và đưa các hệ thống số đó vào ứng dụng thực tế.

Khác với C hay C++ , các câu lệnh của VHDL xảy ra đồng thời (song song nhau)

chứ không theo trình tự.

Một trong những tiện ích của VHDL là cho phép tổng hợp thiết kế hoặc hệ thống

trong một hệ ASIC và VHDL là một ngôn ngữ độc lập chuẩn các nhà công nghệ nên

chúng có khả năng kế thừa cao.

Một số ưu điểm của VHDL:

-

Tính công cộng: Ngôn ngữ VHDL hiện nay là một tiêu chuẩn của IEEE và

nhận được sự hỗ trợ của nhiều nhà sản xuất thiết bị cũng như nhiều nhà cung

cấp công cụ thiết kế mô phỏng hệ thống.

-

Khả năng hỗ trợ nhiều công nghệ và phương pháp thiết kế: Dựa vào thư viện

có sẵn, VHDL cho phép người dùng lựa chọn phương pháp thiết kế từ trên

xuống hoặc là thiết kế từ dưới lên.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 5/61

-

Độc lập với công nghệ: Ngôn ngữ mô tả phần cứng VHDL hoàn toàn độc lập

với công nghệ chế tạo phần cứng vì vậy một thiết kế hệ thống ở mức cổng

dùng ngôn ngữ VHDL có thể được chuyển thành các bản tổng hợp mạch

khác nhau tùy thuộc vào công nghệ chế tạo phần cứng.

-

Khả năng mô tả mở rộng: Sử dụng một cú pháp chặt chẽ thống nhất, VHDL

có khả năng mô tả hoạt động của hệ thống trên nhiều mức khác nhau. VHDL

còn hỗ trợ mô tả hoạt động của phần cứng từ mức hệ thống số cho đến mức

cổng.

-

Khả năng trao đổi kết quả: Các kết quả mô tả hệ thống có thể được trao đổi

với nhau giữa các nhà thiết kế sử dụng các công cụ khác nhau nhưng cùng

thiết kế chung tiêu chuẩn VHDL.

-

Khả năng hỗ trợ thiết kế mức lớn và khả năng sử dụng lại các thiết kế: Ngôn

ngữ VHDL có nhiều tính năng hỗ trợ việc quản lý, chia sẻ thiết kế và VHDL

cũng cho phép dùng lại các phần thiết kế đã có sẵn.

1.1.4 Công cụ thiết kế Alliance

Là mộ phần mềm rất mới ở Việt Nam, Alliance là phần mềm bản quyền mở, được

phát triển bởi trường Đại Học Pierre et Marie Curei University ở Pháp, nhằm mục

đích tạo ra một công cụ thiết kế chip hoàn chỉnh cho sinh viên và những người

nghiên cứu thiết kế chip sử dụng. Phần mềm Alliance là một gói công cụ CAD hoàn

chỉnh cho việc mô tả phần cứng và nó cung cấp đầy đủ các công cụ thiết kế vi mạch

VLSI cũng như các công cụ để kiểm tra thiết kế.

Mốt vài công cụ Alliance sử dụng trong thiết kế:

Vasy: Phân tích và chuyển đổi VHDL, là bước đầu tiên đưa thông tin vào

alliance để xử lí.

Asimut: Biên dịch và mô phỏng VHDL.

Boog: Tổng hợp, cho ra các thông số của mạch thiết kế.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 6/61

Xsch: Xem mạch schematic của thiết kế

Ocp: Đặt và sắp xếp các linh kiện vào mạch cho hợp lí.

Nero: Dùng để nối dây, nối các linh kiện lại với nhau.

DRC: Dùng để kiểm tra xem thiết kế có đúng theo các luật thiết kế đã được

đề ra hay không.

LVS: Kiểm tra layout có đúng với mạch đã thiết kế không.

Cougar: Có tác dụng kết xuất, tổng hợp sơ đồ mạch.

Graal: Giao diện thiết kế vật lý, xem layout của mạch.

Ngoài ra, Phần mêm Alliance còn cung cấp các công cụ có chức năng tối ưu thiết kế

của người dùng:

Loon: Tối ưu thiết kế sơ đồ mạch.

Boom: Phân tích bước chuyển thanh ghi và tối ưu hành vi.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 7/61

Behavior

view

Boom

Asimut

Structural

view

Boog

Loon

LVX

Cougar

Ocp

Nero

Druc

(DRC)

Physical

view

Graal

Hình 2-2: Các công cụ liên kết với nhau trên Alliance

1.5 Kỹ thuật thiết kế chip CMOS

Quy trình cơ bản để thiết kế chip bao gồm 2 bước chính: Thiết kế luận lý và thiết kế

vật lý.

Thiết kế luận lý: được chia làm 3 loại.

Thiết kế số:

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 8/61

Ở thiết kế này chỉ quan tâm đến chức năng của mạch mà không quan tâm đến cấu

tạo chi tiết của mạch. Thiết kế số còn được gọi là thiết kế mức chuyển thanh ghi

RTL. Thiết kế sử dụng ngôn ngữ mô tả phần cứng VHDL, Verilog….

Sau khi thiết kế mức chuyển thanh ghi hoàn thành, thiết kế RTL sẽ được mô phỏng

để kiểm tra độ chính xác. Các công cụ phổ biến được dùng để mô phỏng RTL là

ModelSim, VSC, NC-VHDL, NC-Verilog. Sau cùng thiết kế RTL được tổng hợp

thành các cổng logic cơ bản: AND, NOT, ….

Nhìn chung thiết kế số được hỗ trợ phần lớn bới các công cụ, phần mềm thiết kế.

Thiết kế tương tự:

Thiết kế này đòi hỏi kinh nghiệm của người thiết kế và chủ yếu được thực hiện bởi

con người. Dựa vào kinh nghiệm người thiết kế sẽ lựa chọn vị trí sắp xếp linh kiện,

cấu trúc của con chip sao cho hợp lý.

Thiết kế hỗn hợp:

Các con chip thuộc thiết kế này thường rất phức tạp khi chứa đồng thời các khối

analog và digital.

Ở thiết kế này, người thiết kế phải chú ý đến sự ảnh hưởng qua lại giữa các khối

digital và analog để đảm bảo thiết kế hoạt động tốt và ổn định.

Thiết kế vật lý

Thiết kế vật lý được thực hiện dựa trên kết quả tổng hợp sơ đồ mạch từ thiết kế luận

lý và gồm 2 phần chính: Thiết kế layout và kiểm tra DRC, LVS.

Thiết kế layout

Thiết kế layout phải tuân theo các qui luật của các công ty sản xuất, các quy luật

này tùy thuộc vào công nghệ của công ty thiết kế.

Kiểm tra DRC và LVS

DRC: Kiểm tra xem mạch đã thiết kế có đúng các luật thiết kế hay không và có thể

đem đi sản xuất hay không.

LVS: Kiểm tra và so sánh sơ đồ mạch từ thiết kế luận lý và sơ đồ mạch từ thiết

kế vật lý.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 9/61

Hình 2-3: Quy trình thiết kế luận lý và thiết kế vật lý

CHƯƠNG 3. THIẾT KẾ LÕI IP CHO

MẠNG NƠ RON

1.6 Tổng quan về mạng nơ ron nhân tạo

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 10/61

Mạng nơ ron nhân tạo ( Artificial Nerual Network – ANN ) là mô hình học tập

thống kê, xử lý thông tin được mô phỏng dựa trên hoạt động của hệ thống thần kinh

sinh học. Mạng nơ ron nhân tạo được tạo nên từ một lượng lớn các nơ ron kết nối

với nhau thông qua các liên kết ( trọng số liên kết) làm việc như một thể thống nhất

để giải quyết mốt vấn đề cụ thể nào đó.

Trong một vài năm trở lại đây mạng nơ ron đã được con người áp dụng thành công

trong nhiều lĩnh vực khác nhau như: y tế, vật lý, tài chính và nhiều lĩnh vực khác.

Đúng như đã đề cập, bất cứ vấn đề nào liên quan đến dự báo, điều khiển và phân

loại thì mạng nơ ron đều có thể ứng dụng được như: Khả năng nhận dạng mặt người

trong các hệ thống quản lý (quản lý nhân sự ở các công ty, xí nghiệp; quản lý học

sinh, sinh viên trong các trường đại học và cao đẳng…), các ngành khoa học tướng

số, tử vi; khoa học tội phạm, hình sự.

Kết hợp cùng logic mờ, mạng nơ ron nhân tạo đang tạo nên một cuộc cách mạng

trong việc thông minh và vạn năng hóa các bộ điều khiển kỹ thuật cao.

1.7 Cấu trúc tổng quát của một mạng nơ ron nhân tạo

Input

Hidden

Hình 3-1: Cấu trúc tổng quát của một mạng nơ ron [4]

Cấu trúc chung của một mạng nơ ron gồm 3 thành phần: Input layer, output layer và

hidden layer.

Inputs: Mỗi input tương ứng một thuộc tính của dữ liệu.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 11/61

Hidden: lớp ẩn hidden layer gồm các nơ ron, lớp này có công dụng nhận các

dữ liệu từ lớp layer trước và chuyển đổi dữ liệu này cho lớp tiếp theo xử lý.

Trong một mạng nơ ron có thể có nhiều hidden layer.

Output: Sau khi dữ liệu từ input layer đi vào và được xử lý xong ở hidden

layer, output layer sẽ xuất ra một giải pháp, kết quả cho vấn đề.

1.8 Quá trình xử lý thông tin của một mạng nơ ron

Hình 3-2: Quá trình xử lý thông tin của một mạng nơ ron [4]

Các input đầu vào (x1, x2, x3…) và các trọng số tương ứng (w1, w2 ,w3) được đưa

vào một khối gọi là summation function.

Summation function: Nhiệm vụ thực hiện tính tổng trọng số được đưa vào mỗi nơ

ron. Hàm tổng của một nơ ron đối với n input được tính theo công thức sau:

I=

Transfer function: Hàm tổng (Summation function) của một nơ ron cho biết khả

năng kích hoạt của nơ ron đó còn gọi là kích hoạt bên trong (internal activation).

Các nơ ron này có thể sinh ra một output hoặc không, nói cách khác là transfer

function quyết định có thể output của một nơ ron có được chuyển đến layer kế tiếp

trong mạng nơ ron hay không.

Đôi khi thay vì sử dụng transfer function người ta sử dụng giá trị ngưỡng threshold

để kiểm soát, quyết định các output của các nơ ron tại một layer nào đó trước khi

chuyển đến các layer kế tiếp.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 12/61

1.9 Huấn luyện mạng nơ ron

Mạng nơ ron nhân tạo mô phỏng theo việc xử lý thông tin của não người, vì vậy đặc

trưng cơ bản của mạng nơ ron là khả năng học và tái tạo hình ảnh dữ liệu khi đã

học. Mạng nơ ron có 3 kiểu học chính là: Học có giám sát, học không có giám sát

và học tăng cường.

Học có giám sát: Phương pháp học này có một thành phần không thể thiếu

đó là người thầy. Người thầy có kiến thức về môi trường được thể hiện qua

một tập hợp các cặp đầu vào và đầu ra đã được biết trước. Mạng nơ ron ở

đây đóng vai trò là hệ thống học sẽ phải tìm cách thay đổi các tham số bên

trong mình (các trọng số và ngưỡng) để tạo nên một ánh xạ có khả năng ánh

xạ các đầu vào thành các đầu ra mong muốn.

Học không có giám sát: Sự khác biệt giữa học không có giám sát và học có

giám sát là đầu ra đúng tương ứng cho mỗi đầu vào là không biết trước.

Trong học không có giám sát, một tập dữ liệu đầu vào được thu thập và được

xem như là một tập các biến ngẫu nhiên.

Học tăng cường: Phương pháp học này có chiến lược xây dựng là thông qua

quan sát. Ví dụ như trường hợp là trong một khu rừng, một con nai đang bị

một con cọp dí, nếu rẽ trái con sẽ có một con suối và con nai có thể nhảy qua

để cắt đuôi con cọp, nhưng nếu rẽ phải sẽ có một cái vực và con nai không

thể thoát. Vì vậy mạng nơ ron sẽ phải quan sát môi trường xung quanh, thu

thập thông tin và đưa ra các quyết định. Nếu mạng nơ ron quan sát không tốt,

Input

1.10

đưa ra những quyết định sai nó sẽ phải điều chỉnh các trọng số để từ đó đưa

timer

ra các quyết định khác.

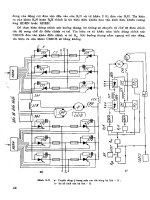

Sơ đồ khối mạng nơ ron

Input

Input

alpha

timer

timer

alpha

Addition and Comparison

alpha

Input

timer

Input

Thiết

kế lõi IP cho timer

mạng nơ ron công nghệ 0.5 um

Addition and

Input

timer

alpha

alpha

Comparison

Inhibit

Output

Outpu

Inhibi

ĐỒ ÁN TỐT NGHIỆP

Trang 13/61

Trọng số weight

Input

alpha

timer

Addition and

Trọng số weight

Input

Comparison

Inhibi

t

Outpu

timer

t

Trọng số weight

alpha

Hình 3-3: Sơ đồ khối mạng nơ ron

Input: Các thông số, dữ liệu được đưa vào. Đây là các thông số quyết định đến việc

dự đoán của con chip.

Trọng số weight: Thể hiện độ quan trọng, sức nặng của các input.

Timer: Bộ định thời hay còn gọi là bộ đếm xung, dùng để tạo 1 khoảng thời gian

ngắt giữa các đầu vào input.

Alpha: Thực hiện hàm alpha function tạo 1 xung hướng lên thật nhanh để mô

phỏng thật giống não người.

Alpha Function: f(x) = x * e-x

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 14/61

Hình 3-4: Mô tả tín hiệu não người [4]

Hình 35: Mô

tả tín

hiệu

được

khối

alpha

xử lý [4]

Addition and Comparison: Tổng hợp các input với weight rồi so sánh với 1

ngưỡng nào đó, quyết định dự đoán của con chip.

Inhibit: Hoạt động như 1 cái chốt, trong khi các khối đang xử lý dữ liệu, khối

inhibit sẽ chặn không cho khối timer đếm tiếp, không cho tín hiệu tiếp theo nhận

vào nhằm mục địch chống nhiễu dữ liệu, khi tín hiệu trước đã xử lý xong khối

inhibit sẽ kích 1 xung lại cho khối timer, khối timer khi được kích sẽ hoạt động tiếp,

bắt đầu đếm để nhận các input kế tiếp.

1.11

Quy trình thiết kế chip cho mạng nơ ron

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 15/61

Thiết lập ý tưởng

Thiết kế layout

Viết code

Kiểm

tra

Kiểm

tra DRC

DRC

Kết xuất

Kết xuất

mạch

mạch

Thiết kế vật lý

Thiết kế luận lý

Mô phỏng code

Thi

ết

kế

Tổng hợp RTL

Kiểm

tra

Kiểm

tra LVS

LVS

Thiết kế mạch

Mô phỏng

Mô phỏng

tổng

tổng

Mô phỏng mạch

tạo/sản

ChếChế

tạo/sản

xuất

xuất

Hình 3-6: Quy trình thiết kế chip cho mạng nơ ron

Thiết lập ý tưởng

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

vật

lý

ĐỒ ÁN TỐT NGHIỆP

Trang 16/61

Đây là bước khởi tạo, ở đây chúng ta hình dung ra công dụng của con chíp để thành

lập ý tưởng thiết kế của mình, xác định các chức năng cần phải làm và các thông số

cần phải có để thiết kế con chip.

Mô tả phần cứng

Sử dụng ngôn ngữ mô tả phẩn cứng để mô tả chức năng của con chip, đáp ứng được

các yêu cầu của con chip cần thiết kế. Hai ngôn ngữ mô tả phần cứng phổ biến hiện

nay là Verilog và VHDL.

Mô phỏng code

Sau khi đã hoàn thành việc viết code, bước mô phỏng này giúp kiểm tra code đã

viết, kiểm tra dạng sóng, các thông số đầu vào, các chức năng của con chip đã được

mô tả bằng code.

Tổng hợp RTL

Tổng hợp RTL hay gọi là tổng hợp mức chuyển thanh ghi, tổng hợp này được chạy

hoàn toàn trong máy.

Thiết kế mạch

Thiết kế mạch logic dựa vào bảng mô tả phần cứng, sử dụng các kết quả của tổng

hợp RTL kết hợp với thư viện có sẵn trong Alliance (thư viện chứa các cổng logic).

Mô phỏng mạch

So sánh với dạng sóng của mô phỏng code xem còn chính xác, còn đúng với ý

tưởng, chức năng của con chip đang thực hiện. Nếu không đúng, phải thực hiện

thiết kế lại.

Thiết kế layout

Đặt các cổng như cổng And, Or, Not… sao cho hợp lý, phù hợp để dễ thực hiện

bước nối dây các cổng. Đây là bước hoàn thiện layout, xuất các chân của con chip

đã thiết kế.

Kiểm tra DRC (Design Rule Check)

Dùng luật thiết kế (công nghệ 0.5 um) để kiểm tra layout đã hoàn thành xem có

đúng luật thiết kế không, nếu đúng có thể đem đi sản xuất, nếu sai phải thực hiện

thiết kế lại.

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um

ĐỒ ÁN TỐT NGHIỆP

Trang 17/61

Kết xuất mạch

Sử dụng layout đã thiết kế để kết xuất ra mạch hoàn chỉnh. Mạch này khác layout ở

điểm là có các thông số delay, điện dung kí sinh….

Kiểm tra LVS ( Layout Versus Schematic)

Còn gọi là kiểm tra layout so với mạch, kiểm tra xem mạch thiết kế có giống với

layout hay không.

CHƯƠNG 4. KẾT QUẢ THU ĐƯỢC

1.12

Kết quả thiết kế luận lý

1.1.5 Mô phỏng dạng sóng

Thiết kế lõi IP cho mạng nơ ron công nghệ 0.5 um