THIẾT kế và LAYOUT MẠCH TÍCH hợp điểm ẢNH APS CHO CAMERA CMOS

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (2.47 MB, 78 trang )

..

TRƢỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI

VIỆN ĐIỆN TỬ - VIỄN THÔNG

ĐỒ ÁN

TỐT NGHIỆP CAO HỌC

Đề tài:

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP

ĐIỂM ẢNH APS CHO CAMERA CMOS

Sinh viên thực hiện:

Lớp:

NGUYỄN ANH TUẤN

11BKTĐT

Giảng viên hƣớng dẫn: TS. VÕ LÊ CƢỜNG

Hà Nội, 11-2013

BỘ GIÁO DỤC VÀ ĐÀO TẠO

TRƢỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI

--------------------------------------------------

CỘNG HỊA XÃ HƠI CHỦ NGHĨA VIỆT NAM

Độc lập - Tự do - Hạnh phúc

---------------------------------

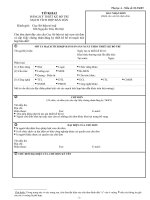

NHIỆM VỤ ĐỒ ÁN TỐT NGHIỆP

Họ và tên sinh viên: .…………….………….…….. Số hiệu sinh viên: ………………

Khố:…………………….Viện: Điện tử - Viễn thơng Ngành: ……………….........

1. Đầu đề đồ án:

………………………………………………..…………………………………………………………………………………

……………………………………………………………………………………………………………..………....................

2. Các số liệu và dữ liệu ban đầu:

……………………………………..……………………………………………..……..……………………………………....

……………………………………………………………………………………………………………………………….…..

………………………..…………………………………………………………………………………………………………

3. Nội dung các phần thuyết minh và tính tốn:

………………………………………………………………………………………………………………..….………………

……………………………………………………………………………………………………………………..….…………

……………………………………………………………………………………………………………………………..….…

…………………………………………………………………………………………

4. Các bản vẽ, đồ thị ( ghi rõ các loại và kích thước bản vẽ ):

………………………………………………………………………………………………………………………..….………

…………………………………………………………………………………………………………………..……….………

………………………………………………………………………………………………….

5. Họ tên giảng viên hướng dẫn: ………………………………………………………..………………………

6. Ngày giao nhiệm vụ đồ án: ………………………………………………….……………………

7. Ngày hồn thành đồ án: ………………………………………………………………………..……………….

Ngày

Chủ nhiệm Bộ mơn

Sinh viên đã hoàn thành và nộp đồ án tốt nghiệp ngày

tháng

năm

Giảng viên hƣớng dẫn

tháng

năm

Cán bộ phản biện

BỘ GIÁO DỤC VÀ ĐÀO TẠO

TRƢỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI

---------------------------------------------------

BẢN NHẬN XÉT ĐỒ ÁN TỐT NGHIỆP

Họ và tên sinh viên: ....................................................................... Số hiệu sinh viên: ...........................

Ngành: .................................................................................................. Khoá: ....................................................

Giảng viên hƣớng dẫn:.............................................................................................................................................. .........

Cán bộ phản biện: ........................................................................................................................... ......................................

1. Nội dung thiết kế tốt nghiệp:

............................................................................................................................. .............................................................................

............................................................................................................................. .............................................................................

....................................................................................................................................................................... ...................................

..........................................................................................................................................................................................................

............................................................................................................................. .............................................................................

............................................................................................................................. .............................................................................

............................................................................

2. Nhận xét của cán bộ phản biện:

............................................................................................................................. .............................................................................

................................................................................................................................................................................... .......................

............................................................................................................ ..............................................................................................

............................................................................................................................. .............................................................................

............................................................................................................................. .............................................................................

........................................................................................................................................... ...............................................................

................................................................................................................................................................................................. .........

.......................................................................................................................... ................................................................................

Ngày

tháng

năm

Cán bộ phản biện

( Ký, ghi rõ họ và tên )

Lời nói đầu

***

Hiện nay trong ngành cơng nghiệp camera có hai công nghệ phát triển chip là

CMOS và CCD. Đây là hai cơng nghệ cảm biến hình ảnh chính hiện nay. Cả hai đều có

những ƣu và nhƣợc điểm và việc lựa chọn công nghệ nào phụ thuộc vào ứng dụng,

cũng nhƣ nhà sản xuất. Cảm biến hình ảnh có chức năng chuyển đổi tín hiệu quang

thành tín hiệu điện. Điểm khác biệt giữa CCD và CMOS là khâu đọc dữ liệu từ các ơ

cảm biến. Ở CCD, điện tích sinh ra ở các bộ thu quang trong suốt quá trình phơi sáng

và đƣợc chuyển đồng thời sang các cột CCD sau khi kết thúc quá trình bắt sáng. Các

điện tích này đƣợc truyền và đọc nối tiếp nhau thơng qua các hàng và cột CCD. Ở cảm

biến ảnh CMOS, thì tín hiệu đƣợc khuyếch đại nhờ một số transistor bên trong điểm

ảnh. Các điểm ảnh trong ma trận đƣợc đánh địa chỉ thơng qua các hàng và tín hiệu điện

tích đƣợc đọc ra từ mỗi điểm ảnh qua các cột. Quá trình đọc ra đƣợc thực hiện bằng

cách truyền 1 hàng mỗi lần tới các tụ lƣu ở cột sau đó đọc ra ngồi, vì vậy tốc độ đọc

của CMOS cao hơn hẳn CCD. Ngoài ra, máy ảnh sử dụng chip CMOS có một ƣu điểm

nổi bật là tiêu thụ điện năng ít hơn nhiều so với CCD.

Nếu nhƣ trƣớc đây chip cảm biến hình ảnh CMOS đƣợc cho là chỉ phù hợp lắp

trên các dòng máy số rẻ tiền, có độ phân giải thấp hơn hẳn so với chip cảm biến CCD.

Chip cảm biến CCD tỏ ra có ƣu thế hơn bởi khả năng nhạy sáng cao, có thể tái hiện

những bức ảnh có độ phân giải lớn, thể hiện đƣợc các dải màu liên tục. Trong khi cơng

nghệ chế tạo chíp cảm biến CMOS chƣa hồn thiện nên kích thƣớc transistor lớn,

photodiode nhỏ làm cho độ nhạy sáng kém. Độ phân dải và khả năng hiện thị mầu của

CMOS thấp nên ảnh thu đƣợc dễ bị rạn. Do vậy dù chi phí sản xuất CCD rất đắt so với

sản xuất CMOS, CCD vẫn vƣợt mặt và trở thành thành phần chủ yếu trong các máy

ảnh số. Gần đây các kiến trúc điểm ảnh của công nghệ CMOS đã dần khắc phục đƣợc

các nhƣợc điểm trên và cùng với các ƣu thế vốn có là: khả năng tích hợp, tốc độ cao và

công suất thấp, điểm ảnh dùng công nghệ CMOS đang dần chiếm lại thị trƣờng.

Với lí do trên luận văn này nghiên cứu và thiết kế điểm ảnh camera dùng cơng

nghệ CMOS trên phần mềm Cadence Virtuoso. Trong q trình thực hiện đồ án tốt

nghiệp tại AICS-Group tôi đã nhận đƣợc sự giúp đỡ chỉ bảo tận tình của Tiến sĩ Võ Lê

Cƣờng và các em sinh viên, đặc biệt là em Nguyễn Văn Duẩn. Tôi xin gửi lời cảm ơn

trân trọng nhất tới Tiến sĩ Võ Lê Cƣờng, em Nguyễn Văn Duẩn và toàn thể thành viên

AICS-Group đã giúp đỡ tơi trong q trình thực hiện đồ án này.

Tóm tắt đồ án

***

Đồ án đề cập đến vấn đề thiết kế điểm ảnh APS sử dụng công nghệ CMOS

130nm với hai phƣơng pháp là sử dụng transistor NMOS và PMOS đồng thời chỉ ra ƣu

nhƣợc điểm trong từng phƣơng pháp thiết kế. Đề tài này tập trung thiết kế và mô phỏng

mạch schematic và layout điểm ảnh APS theo hai phƣơng pháp nêu trên.

Mạch sử dụng transistor NMOS có dải động thấp nhƣng độ nhạy cao (tỉ lệ Fill

factor = 68.96%) thích hợp cho những camera hoạt động ở điều kiện thiếu sáng và dải

ánh sáng đến camera hẹp. Mạch sử dụng transistor PMOS ngƣợc lại có độ nhạy thấp (tỉ

lệ Fill factor = 55.88%) và dải động cao nên thích hợp cho những camera hoạt động ở

điều kiện ánh sáng không quá yếu và dải ánh sáng đến camera rộng. Mỗi thiết kế đều

có ƣu điểm và nhƣợc điểm riêng nên việc lựa chọn thiết kế nào tùy thuộc vào yêu cầu

thiết kế và yêu cầu của ứng dụng.

Bố cục của đồ án ngoài phần mở đầu và kết luận sẽ gồm 5 chƣơng :

Chƣơng 1 Giới thiệu chung về công nghệ camera CMOS.

Chƣơng 2 Cơ sở lý thuyết về thiết kế điểm ảnh camera dùng công nghệ CMOS.

Chƣơng 3 Nghiên cứu các kiến trúc điểm ảnh cho camera CMOS.

Chƣơng 4 Thiết kế điểm ảnh APS.

Chƣơng 5 Kết luận và hƣớng phát triển của đề tài.

ABSTRACT

***

The thesis presents design of APS using 130nm CMOS technology with two

approaches using NMOS and PMOS for source follower seperatly. Advantages and

disadvantages of each method are discussed as well. The thesis tocuses on designing

and simulating the schematic and layout circuit of the APS based on the two above

mentioned techiques.

Circuits using NMOS transistors have low dynamic range but high sensitivity (fill

factor = 68.96%) cameras suitable for operation in low light conditions and a narrow

strip of light to the camera. PMOS transistor circuits using reverse low sensitivity (Fill

Factor = 55.88%) and high dynamic range camera is suitable for operation in low-light

conditions not too weak and broad band light to the camera. Each design has its own

advantages and disadvantages, so the choice depends on the design requirements and

design requirements of the application.

The thesis is organized into 5 sections:

Chapter I: Instroduction.

Chapter II: Theoretical basis

Theoretical basis for the design of CMOS camera technology used.

Chapter III: Look at the pixel architecture for CMOS camera.

Chapter IV: Design of APS.

Chapter V: Conclusion and future work.

MỤC LỤC

Lời nói đầu .................................................................................................................................. 4

Tóm tắt đồ án .............................................................................................................................. 6

Danh mục hình vẽ ..................................................................................................................... 10

Danh mục bảng biểu ................................................................................................................. 12

Danh mục từ viết tắt .................................................................................................................. 13

CHƢƠNG 1 : GIỚI THIỆU CHUNG ........................................................................................ 1

1.1 Đặt vấn đề ............................................................................................................................. 1

1.2 Mục tiêu đề tài ...................................................................................................................... 1

1.3 Phƣơng pháp nghiên cứu ...................................................................................................... 2

CHƢƠNG 2 : CƠ SỞ LÝ THUYẾT .......................................................................................... 3

2.1 Giới thiệu chung về một hệ thống camera ............................................................................ 3

2.2 Hoạt động của cảm biến hình ảnh ......................................................................................... 4

2.2.1 Cảm biến dùng công nghệ CCD .................................................................................. 5

2.2.2 Cảm biến ảnh CMOS ................................................................................................. 10

2.2.3 Các thông số của cảm biến ảnh .................................................................................. 14

2.3 Các linh kiện trong mạch .................................................................................................... 20

2.3.1 Photodiode ................................................................................................................. 20

2.3.2 Transistor MOSFET .................................................................................................. 26

2.3.2.1 Cấu tạo .............................................................................................................. 26

2.3.2.2 Các chế độ hoạt động ........................................................................................ 27

CHƢƠNG 3: NGHIÊN CỨU LỰA CHỌN KIẾN TRÚC ĐIỂM ẢNH .................................. 33

3.1 Lý thuyết cấu trúc điểm ảnh PPS ........................................................................................ 33

3.2 Lý thuyết cấu trúc điểm ảnh APS ....................................................................................... 36

3.2.1 Mạch nguyên lí cơ bản APS ..................................................................................... 36

3.2.2 Các kiến trúc APS ..................................................................................................... 37

3.3 Lý thuyết cấu trúc điểm ảnh DPS ....................................................................................... 40

3.4 Ƣu nhƣợc điểm các kiến trúc điểm ảnh .............................................................................. 42

CHƢƠNG 4 THIẾT KẾ ĐIỂM ẢNH APS .............................................................................. 43

4.1 Mô phỏng mạch nguyên lí 3T-APS .................................................................................... 44

4.2 Mơ phỏng mạch ngun lí 4T-APS .................................................................................... 47

4.2.1 Mơ phỏng và layout mạch ngun lí 4T-APS sử dụng NMOS source follower. .... 47

4.2.2 Mơ phỏng và layout mạch ngun lí 4T-APS sử dụng PMOS source follower có

NMOS shutter và NMOS row-select. ...................................................................................... 52

4.2.3 Mơ phỏng và layout mạch ngun lí 4T-APS sử dụng PMOS source follower có

NMOS shutter và PMOS row-select. ........................................................................................ 57

4.4 PHÂN TÍCH VÀ ĐÁNH GIÁ KẾT QUẢ ......................................................................... 61

CHƢƠNG 5 KẾT LUẬN VÀ HƢỚNG PHÁT TRIỂN ........................................................... 63

5.1 Mục tiêu và kết quả đạt đƣợc. ............................................................................................. 63

5.2 Hƣớng phát triển ................................................................................................................. 64

Danh mục hình vẽ

Hình 2. 1: Một hệ thống camera trong thực tế ............................................................................ 3

Hình 2. 2: Hoạt động CCD 3 pha................................................................................................ 6

Hình 2. 3: Q trình truyền tín hiệu trong cảm biến ảnh CCD ................................................... 7

Hình 2. 4: Sơ đồ khối cảm biến hình ảnh CMOS ..................................................................... 11

Hình 2. 5: Điểm ảnh PPS và APS ............................................................................................. 12

Hình 2. 6: APS dùng photogate ................................................................................................ 13

Hình 2. 7: Điểm ảnh DPS ......................................................................................................... 14

Hình 2. 8: Mơ hình điểm ảnh cảm biến CMOS ........................................................................ 15

Hình 2. 9: Đồ thị của SNR theo iph ........................................................................................... 17

Hình 2. 10 Đồ thị biểu diễn SNR và iph .................................................................................... 18

Hình 2. 11: Đồ thị DR theo thời gian phơi sáng ....................................................................... 20

Hình 2. 12: Hoạt động của photodiode ..................................................................................... 22

Hình 2. 13: Mơ hình photodiode trong mơ phỏng .................................................................... 23

Hình 2. 14: Photodiode với q trình phơi sáng ....................................................................... 25

Hình 2. 15: Đồ thị Vd theo thời gian ........................................................................................ 25

Hình 2. 16: Cấu tạo transistor NMOS....................................................................................... 27

Hình 2. 17: Cấu tạo của transistor MOSFET loại NMOS ........................................................ 27

Hình 2. 18: Đồ thị đặc tuyến hoạt động của transistor NMOS ................................................. 28

Hình 2. 19: Mơ hình NMOS khi VGS 0 .................................................................................. 29

Hình 2. 20: Mơ hình tín hiệu nhỏ của transistor mắc theo sơ đồ S chung ................................ 31

Hình 3. 1: Cấu trúc APS và biểu đồ thời gian quá trình đọc và phơi sáng ............................... 36

Hình 3. 2: Pixel trong kiến trúc 3T-APS .................................................................................. 37

Hình 3. 3: Pixel trong kiến trúc 4T-APS .................................................................................. 39

Hình 3. 4: Điểm ảnh DPS ......................................................................................................... 41

Hình 4. 1: Mạch nguyên lý 3T-APS sử dụng NMOS source follower ..................................... 44

Hình 4. 2: Biểu đồ thời gian điện áp trên net15 của mạch APS sử dụng NMOS source follower

.................................................................................................................................................. 46

Hình 4. 3: Mạch APS sử dụng NMOS source follower có NMOS shutter và NMOS rowselect ......................................................................................................................................... 47

Hình 4. 4: Biểu đồ thời gian các xung đầu vào ......................................................................... 48

Hình 4. 5: Biểu đồ thời gian điện áp trên FD của mạch APS-4T sử dụng NMOS source

follower ..................................................................................................................................... 49

Hình 4. 6: Biểu đồ thời gian điện áp ra của mạch APS-4T sử dụng NMOS source follower .. 50

Hình 4. 7: Mạch layout APS-4T sử dụng NMOS source follower ........................................... 51

Hình 4. 8: Mạch APS-4T sử dụng PMOS source follower có NMOS shutter và NMOS rowselect ......................................................................................................................................... 52

Hình 4. 9: Biểu đồ thời gian điện áp trên net13 của mạch APS-4T sử dụng PMOS source

follwer NMOS shutter và NMOS row-select ........................................................................... 54

Hình 4. 10: Giá trị đầu ra của mạch APS-4T sử dụng PMOS source follwer NMOS shutter và

NMOS row-select ..................................................................................................................... 55

Hình 4. 11: Mạch layout APS sử dụng PMOS source follwer NMOS shutter và NMOS rowselect ......................................................................................................................................... 56

Hình 4. 12: Mạch APS sử dụng PMOS source follower có NMOS shutter và PMOS rowselect. ........................................................................................................................................ 57

Hình 4. 13: Biểu đồ thời gian điện áp trên FD của mạch APS-4T sử dụng PMOS source

follower có NMOS shutter và PMOS row-select. .................................................................... 58

Hình 4. 14: Giá trị đầu ra của mạch APS sử dụng PMOS source có NMOS shutter và PMOS

row-select. ................................................................................................................................. 59

Hình 4. 15: Mạch layout APS sử dung PMOS source follower và row-select ......................... 60

Danh mục bảng biểu

Bảng 2. 1: Bảng các giá trị η và tỉ lệ điện tích ở đầu ra tƣơng ứng trong trƣờng hợp xấu nhất . 8

Bảng 4. 1: Kết quả mô phỏng mạch schematic ......................................................................... 61

Bảng 4. 2: Độ nhạy sáng giữa mạch sử dụng NMOS và PMOS .............................................. 61

Danh mục từ viết tắt

CCD

: Charge Coupled Device

CMOS

: Complementary Metal Oxide Semiconductor

PPS

: Passive Pixel Sensor

APS

: Active Pixel Sensor

DPS

: Digital Pixel Sensor

SNR

: Signal to Noise Ratio

DR

: Dynamic Range

LOFIC

: Lateral Overflow Capacitor

TTS

: Time to Saturation

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

CHƢƠNG 1 : GIỚI THIỆU CHUNG

1.1 Đặt vấn đề

Bộ phận cảm biến hình ảnh là trái tim của một hệ thống camera số, có chức

năng chuyển đổi tín hiệu quang thành tín hiệu điện. Có 2 cơng nghệ cảm biến hình

ảnh chính là CCD (Charge Coupled Device) và công nghệ CMOS (Complementary

Metal Oxide Semiconductor). Trƣớc đây CCD chiếm ƣu thế nhờ vào chất lƣợng

hình ảnh tốt, khả năng chống nhiễu cao hơn CMOS. Tuy nhiên CMOS lại có ƣu thế

về khả năng tích hợp, tốc độ cao và cơng suất thấp thích hợp cho các thiết bị cầm

tay, điện thoại… Gần đây các kiến trúc điểm ảnh của công nghệ CMOS đã dần khắc

phục đƣợc các nhƣợc điểm về chất lƣợng hình ảnh và cùng với các ƣu thế vốn có,

điểm ảnh dùng cơng nghệ CMOS đang dần chiếm lại thị trƣờng.

1.2Mục tiêu đề tài

-

Nghiên cứu lý thuyết cấu trúc cơ bản của điểm ảnh APS (Active Pixel

Sensor) cho Camera CMOS.

-

Nghiên cứu lý thuyết ƣu nhƣợc điểm khi sử dụng NMOS và PMOS trong cấu

trúc điểm ảnh APS.

-

Thiết kế, mô phỏng mạch nguyên lý 2 loại điểm ảnh APS: sử dụng NMOS và

PMOS.

-

Thiết kế layout cho 2 mạch nguyên lý nêu trên.

-

Chứng minh ƣu nhƣợc điểm của NMOS hoặc PMOS thơng qua thiết kế điểm

ảnh APS.

-

Phân tích sự phù hợp của việc sử dụng cấu trúc NMOS/ PMOS cho các ứng

dụng khác nhau.

Page 1

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

1.3Phƣơng pháp nghiên cứu

-

Phƣơng pháp nghiên cứu lý thuyết.

-

Phƣơng pháp nghiên cứu mô phỏng.

-

Phƣơng pháp tham khảo chuyên gia.

Page 2

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

CHƢƠNG 2 : CƠ SỞ LÝ THUYẾT

2.1 Giới thiệu chung về một hệ thống camera

Hình 2. 1: Một hệ thống camera trong thực tế

Camera bao gồm một hệ thống các thành phần hoạt động cùng nhau nhằm thu

lại hình ảnh với chất lƣợng cao nhất. Sơ đồ khối của một hệ thống camera trong thực

tế đƣợc thể hiện trong hình 2.1. Ánh sáng sau khi xuyên qua thấu kính (lens) và bộ

lọc màu (CFA – Color Filter Array) đƣợc chuyển thành tín hiệu điện tại bộ phận

cảm biến (Image Sensor). Tín hiệu điện này sau đó đƣợc khuếch đại ở bộ AGC

(Automatic Gain Control) và sau đó đƣợc chuyển thành tín hiệu số. Cuối cùng tín

hiệu số này đƣợc xử lý và nén để lƣu trữ thành ảnh số.

Với khả năng tích hợp ngày càng cao của cơng nghệ CMOS thì chúng ta có

thể để các mạch AGC, ADC (Analog to Digital Converter), xử lý và nén ảnh vào

cùng một chip. Việc tích hợp phần cảm biến cùng với các mạch xử lý do một số

nguyên nhân vẫn chƣa thực hiện đƣợc một cách triệt để.

Cảm biến hình ảnh đóng một vai trị quan trọng trong việc quyết định chất

lƣợng hình ảnh thu đƣợc. Phần lớn các hệ thống camera trƣớc đây dùng công nghệ

Page 3

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

CCD. Dạng cảm biến hình ảnh này cho phép điện tích thu đƣợc tại bộ thu quang

trong suốt thời gian phơi sáng dịch nối tiếp ra khỏi ma trận điểm ảnh. Chính phƣơng

thức này gây ra cho điểm ảnh dùng công nghệ CCD tốc độ thấp và tiêu thụ công suất

lớn. CCD đƣợc chế tạo với một tiến trình xử lý đặc biệt với một bộ thu quang tối ƣu

có nhiễu rất thấp và tính đồng dạng cao. Vì q trình xử lý này khơng tƣơng thích

với xử lý CMOS chuẩn nên các cảm biến CCD không thể tích hợp với các mạch xử

lý dùng cơng nghệ CMOS.

Các cảm biến CMOS mới phát triển gần đây tƣơng tự với các bộ nhớ số, đọc

ra không mất dữ liệu và có thể hoạt động ở tốc độ rất cao. Cảm biến CMOS có thể

tích hợp vào cùng một chíp với kích thƣớc nhỏ, cơng suất thấp và kèm theo các chức

năng khác. Chính nhờ những ƣu điểm này mà cảm biến CMOS đang ngày càng

đƣợc ứng dụng nhiều vào các ứng dụng trong các điện thoại di động, ô tô,… Tuy

nhiên do vấn đề về nhiễu khi đọc và nhiễu cố định FPN (Fixed Pattern Noise) nên

cảm biến CMOS thƣờng có tỉ lệ tín hiệu trên nhiễu SNR (Signal to Noise Ratio) và

dải động (Dynamic Range) nhỏ hơn so với CCD. Tăng SNR và DR cho cảm biến

CMOS trở thành mục tiêu chung cho ngành công nghiệp và các trung tâm nghiên

cứu hƣớng tới.

2.2 Hoạt động của cảm biến hình ảnh

Trong kiến trúc camera mơ tả tại mục 2.1 thì phần quan trọng nhất là cảm

biến ảnh. Vì vậy trong mục này sẽ tập trung giới thiệu các công nghệ phổ biến về

cảm biến ảnh và các tham số quan trọng của cảm biến ảnh.

Ma trận cảm biến nxm điểm ành nằm trong khoảng 320x240 (QVGA) tới

7000x9000 (dùng trong thiên văn học)

Mỗi điểm ảnh bao gồm 1 bộ thu sáng và mạch đọc (tụ thƣờng với CCD,

transistor MOS trong cảm biến CMOS)

Kích cỡ điểm ảnh nằm trong khoảng 15x15µm2 tới 3x3µm2 (giới hạn bởi dải

động và giá của thiết bị quang)

Page 4

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

Fill factor là tỉ lệ diện tích cảm biến dùng làm bộ thu quang, nằm trong

khoảng 0.2 đến 0.9 ->fill factor cao thì nhạy hơn

Có thể tăng fill factor bằng cách dùng microlens

Sự khác nhau cơ bản giữa cảm biến CCD và CMOS là cấu trúc đọc ra:

Với CCD điện tích đƣợc dịch dần ra ngồi

Với CMOS điện tích hoặc điện áp đƣợc đọc ra bằng cách sử dụng bộ giải mã

hàng và cột – tƣơng tự nhƣ 1 bộ nhớ số nhƣng dữ liệu tƣơng tự đƣợc đọc ra.

Mạch đọc ra bao gồm các thiết bị khác trong điểm ảnh xác định hệ số chuyển

đổi là điện áp ra ứng với mỗi e thu đƣợc tại bộ thu quang (µV/electron)

Từ đáp ứng quang phổ, hệ số chuyển đổi và diện tích của cảm biến, độ nhạy

của nó đƣợc xác định V/Lux.s.

Tốc độ đọc ra xác định tốc độ hình video mà 1 cảm biến có thể hoạt động,

thơng thƣờng khoảng 30 đến 60 hình/s nhƣng tốc độ hình chậm hơn đơi khi phải

dùng do giới hạn băng thông khả dụng (PC camera) và tốc độ hình cao hơn địi hỏi

bởi các ứng dụng trong công nghiệp và quân sự.

2.2.1 Cảm biến dùng công nghệ CCD

Cảm biến ảnh CCD hiện nay vẫn đƣợc ứng dụng rộng rãi trong các hệ thống

camera số. CCD là 1 thanh ghi dịch giá trị tƣơng tự (điện tích) động chế tạo bằng

cách sử dụng các tụ MOS đƣợc đồng bộ hóa sử dụng 2,3 hoặc 4 pha clock – các tụ

này hoạt động ở chế nghèo sâu khi clock ở mức cao.

Sự truyền điện tích từ 1 tụ sang tụ kế tiếp diễn ra phải ở tốc độ đủ lớn để

tránh mất mát do dòng rò nhƣng phải đủ chậm để đảm bảo hệ số chuyển đổi điện

tích cao.

CCD 3 pha đƣợc chế tạo sử dụng 3 lớp polysilicon (để điều khiển clock và

tận dụng trƣờng ở biên)

Hoạt động CCD 3 pha :

Page 5

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

Hình 2. 2: Hoạt động CCD 3 pha

Điểm khác biệt cơ bản giữa CCD và CMOS chính là kiến trúc đọc ra. Với

CCD thì điện tích đƣợc dịch nối tiếp ra ngồi qua các tụ. Hình 2.2 mơ tả quá trình

dịch dữ liệu trong cảm biến ảnh CCD. Hệ thống bao gồm ma trận điểm ảnh và các

hàng, cột CCD phục vụ việc đọc dữ liệu. Trong suốt q trình phơi sáng điện tích

Page 6

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

sinh ra ở các bộ thu quang và đƣợc chuyển đồng thời sang các cột CCD khi kết thúc

q trình bắt sáng. Các điện tích này đƣợc truyền và đọc nối tiếp nhau thông qua các

hàng và cột CCD.

Hình 2. 3: Q trình truyền tín hiệu trong cảm biến ảnh CCD

CCD là một thanh ghi dịch động sử dụng các tụ MOS liền nhau hoạt động ở

các pha khác nhau. Các tụ hoạt động ở vùng nghèo sâu khi clock ở mức cao. Điện

tích chuyển từ một tụ khi clock tƣơng ứng chuyển từ mức cao về mức thấp tới tụ

tiếp theo có clock chuyển từ mức thấp lên cao cùng lúc đó. Trong q trình truyền

hầu hết điện tích truyền rất nhanh bởi lực đẩy giữa các điện tử, những điện tử cịn lại

thì truyền chậm do khuếch tán nhiệt và trƣờng ở biên.

Hệ số truyền điện tích của CCD η

là tỉ số của điện tích tín hiệu đƣợc

truyền từ 1 tầng CCD sang tầng kế tiếp. Hệ số này phải đƣợc điều chỉnh càng cao

càng tốt vì ở cảm biến CCD điện tích đƣợc truyền trên n+m tầng CCD (3x(n+m) lần

Page 7

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

với CCD 3 pha). Ví dụ cảm biến CCD 1024x1024 ta có bảng các giá trị η và tỉ lệ

điện tích ở đầu ra tƣơng ứng trong trƣờng hợp xấu nhất

η

Tỉ lệ ở đầu ra

0.999

0.1289

0.9999

0.8148

0.99999

0.9797

Bảng 2. 1 Bảng các giá trị η và tỉ lệ điện tích ở đầu ra tƣơng ứng trong trƣờng

hợp xấu nhất

Cơ cấu truyền điện tích :

Hầu hết điện tích đƣợc truyền rất nhanh bởi lực đẩy giữa các điện tử (tạo nên

sự trơi giạt ở bên do tự cảm)

Điện tích cịn lại đƣợc truyền chậm bởi khuếch tán nhiệt và trƣờng ở biên.

Hệ số truyền có thể xác định chính xác bằng các thiết bị mơ phỏng 2, 3D

Phân tích đơn giản :

99% điện tích đƣợc truyền đi ngay lập tức, 1% còn lại truyền chậm do khuếch

tán nhiệt.

Tính tốn 1% cuối cùng này cho tồn bộ thời gian truyền và ta có thể viết

Với tstage là thời gian truyền ở 1 tầng CCD, p là số pha CCD đƣợc dùng và

với L là khoảng cách tâm 2 tụ liền kề và Dn là hằng số khếch tán tại bề

mặt. Với η cho trƣớc ta có thể dùng phƣơng trình trên để tìm giới hạn dƣới của thời

gian truyền.

Page 8

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

Phân tích chính xác hơn phải xem xét tới trƣờng tại biên (tăng η) và chế độ

cửa sập trên bề mặt (giảm η)

Trƣờng ở biên có thể tăng bằng cách :

Tăng sự thay đổi vG trong quá trình truyền.

Giảm L (tăng τ)

Giảm khoảng cách giữa các tụ (xấp xỉ độ dày lớp oxide) và chồng lên poly

gates.

Sử dụng đế pha tạp thấp.

Tốc độ đọc ra CCD bị giới hạn bởi kích cỡ mảng và hệ số truyền điện tích cần

thiết.

VD : Xét CCD 3 pha truyền theo đƣờng 1024x1024 với η=0.99997, L=4µm

và Dn=35cm2/s. Tìm tốc độ hình video lớn nhất.

Thời gian truyền CCD hàng giới hạn tốc độ đọc. Để tìm thời gian truyền nhỏ

nhất cho mỗi tầng CCD, tmin, ta dùng phƣơng trình

η = 0.99997 = (1-0.01e (tmin/3τ))3

Từ đó tmin = 37.8ns -> thời gian cần thiết để dịch 1 hàng ra là 37.8ns x 1024 =

38.7µs, bỏ

qua thời gian truyền hàng (từ các CCD cột) ta có tốc độ truyền khung

nhỏ nhất là 39.6ms hay tốc độ hình video lớn nhất là 25 hình/s

Ƣu điểm của CCD:

Chất lƣợng hình ảnh tốt.

CCD đƣợc chế tạo với công nghệ đặc biệt, bộ thu quang đƣợc tối ƣu (nhiễu

rất thấp, tính đồng dạng, QE cao và dịng tối thấp).

Khơng có nhiễu trong q trình truyền điện tích.

Nhƣợc điểm CCD :

Khơng thể tích hợp vào các mạch tƣơng tự và mạch số nhƣ mạch tạo xung

clock, bộ chuyển đổi ADC

Không lập trình đƣợc

Cơng suất tiêu thụ cao

Page 9

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

Tốc độ hình bị giới hạn nhất là với các cảm biến kích thƣớc lớn.

Q trình đọc ra của CCD là mất dữ liệu, tín hiệu chỉ có thể đọc một lần

đồng thời xóa giá trị trong tụ.

2.2.2 Cảm biến ảnh CMOS

Các cảm biến ảnh CMOS đƣợc chế tạo dùng công nghệ CMOS chuẩn mà

không cần hoặc chỉ cần thay đổi rất ít. Các điểm ảnh trong ma trận đƣợc đánh địa

chỉ thông qua các hàng và tín hiệu điện tích hoặc điện áp đƣợc đọc ra từ mỗi điểm

ảnh qua các cột. Quá trình đọc ra đƣợc thực hiện bằng cách truyền 1 hàng mỗi lần

tới các tụ lƣu ở cột sau đó đọc ra ngoài dùng các bộ giải mã và dồn kênh tƣơng tự

nhƣ cấu trúc bộ nhớ. Hình 2.4 mơ tả cấu trúc cảm biến CMOS. Có 3 cấu trúc điểm

ảnh chính là :

PPS (Passive Pixel Sensor)

APS (Active Pixel Sensor)

DPS (Digital Pixel Sensor).

Page 10

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

Hình 2. 4: Sơ đồ khối cảm biến hình ảnh CMOS

Điểm ảnh PPS

PPS chỉ gồm 1 transistor mỗi điểm ảnh. Tín hiệu điện tích ở mỗi điểm ảnh

đƣợc đọc ra qua bộ khuếch đại cột, và quá trình đọc ra này xóa dữ liệu (giống CCD).

PPS có kích thƣớc điểm ảnh nhỏ nên hệ số điền đầy FF lớn nhƣng lại gặp vấn đề về

tốc độ đọc ra chậm và tỉ lệ tín hiệu trên nhiễu SNR thấp. Thời gian đọc ra của PPS

bị giới hạn bởi thời gian truyền tín hiệu từ 1 hàng tới các bộ khuếch đại.

Điểm ảnh APS

APS (Active Pixel Sensor) thƣờng gồm 3 đến 4 transistor mỗi điểm ảnh với

một trong số đó đóng vai trị bộ đệm và khuếch đại. Tín hiệu ra ở photodiode đi qua

một bộ đệm ở mức pixel (source follower) nên q trình đọc ra khơng xóa dữ liệu ở

Page 11

THIẾT KẾ VÀ LAYOUT MẠCH TÍCH HỢP ĐIỂM ẢNH APS CHO CAMERA CMOS

2013

diode. So với PPS thì APS có kích thƣớc điểm ảnh lớn hơn nên tỉ lệ FF nhỏ hơn

nhƣng tốc độ đọc ra cao hơn và SNR cũng lớn hơn.

Hình 2. 5: Điểm ảnh PPS và APS

Hình 2.6 mô tả cấu trúc điểm ảnh APS dùng photogate CMOS. Photogate PG

đƣợc phân cực ở chế độ nghèo sâu trong suốt thời gian phơi sáng và photon sinh ra

điện tích tích lũy dƣới cực của (gate). Sau đó trong q trình đọc điện áp ở

photogate thấp hơn 0V và điện tích đƣợc chuyển qua điểm D (đã đƣợc reset về một

giá trị đã biết trƣớc khi nhận điện tích). Cổng truyền TX có thể chuyển từ mức thấp

lên cao hoặc giữ cố định ở một mức trung gian trong quá trình truyền. Tín hiệu ra

của điểm ảnh là điện áp đã đƣợc biến đổi ở điểm D. Các mạch ngoại vi của APS

dùng photogate tƣơng tự nhƣ APS dùng photodiode.

Page 12