3.1 - Cau truc mach cac Flip FLop pot

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (128.3 KB, 15 trang )

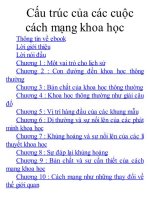

Bài 3.1: Cấu trúc mạch các flip flop

Flip - Flop (FF) là các phần tử nhớ cơ bản, là phần tử có khả

năng lưu trữ (nhớ) một trong hai trạng thái 0 hoặc 1.

FF có từ 1 đến 1 vài đầu vào điều khiển, có 2 đầu ra luôn luôn

Chươnglà Q và Q. Tùy từng loại FF, do chế tạo có thể bản

ngược nhau 3: các mạch Flip flop cơ còn có

đầu vào xóa (thiết lập 0 - Clear), đầu vào thiết lập (thiết lập 1

- Preset). Ngoài ra, FF còn thường hay có đầu vào đồng bộ

(Clock).

Sơ đồ khối tổng quát của 1 FF:

Pr

Các tín hiệu

điều khiĨn

FLIP

FLOP

Ck

Q

Q

Clr

C¸c ký hiƯu vỊ tÝnh tÝch cùc:

Ký hiƯu

TÝnh tÝch cùc cđa tÝn hiƯu

TÝch cùc lµ møc thÊp “L”

TÝch cùc lµ mức cao H

Tích cực là sườn dương của xung nhịp

Tích cực là sườn âm của xung nhịp

.

1. Flip flop RS cơ bản

1.1 Cấu trúc mạch và ký hiệu:

Q

Q

Q

A

S

Q

S

R

B

R

1.2 Nguyên lý làm việc:

a. Hai trạng thái ổn định:

Khi không có tín hiệu, tức là R = S = 1, mạch có hai trạng thái

ổn định - trạng thái 0 và trạng thái 1.

Q = 0, Q = 1 : là trạng thái 0.

Q = 1, Q = 0 : là trạng thái 1.

+ ở trạng thái 0:

Q

A

Q = 0 cổng B ng¾t ⇒ Q = 1

Q = 1 , S = 1 ⇒ cỉng A th«ng ⇒ Q = 0

⇒ Do đó, mạch hoàn toàn tự động duy trì

trạng thái 0.

+ ở trạng thái 1:

S

Q

B

R

Q = 1, R = 1 cỉng B th«ng ⇒ Q = 0

Q = 0 ⇒ cổng A ngắt Q = 1

Do đó, mạch hoàn toàn tự động duy trì trạng thái 1.

b. Không cho phép đưa tín hiệu đồng thời vào cả R và S :

Do đặc tính mạch cổng NAND, khi R = S = 0 th× Q = Q = 1

⇒ Không phải là trạng thái 0.

Không phải là phần tử nhớ.

Không phải là trạng thái 1

c. Bảng chức năng và phương trình đặc trưng:

Kí hiệu:

Qn: Trạng thái hiện tại

Qn+1: Trạng thái tiếp theo.

Quan hệ logic giữa Qn+1 và Qn, R, S biểu thị bằng bảng chức

năng mô tả sự chuyển đổi trạng thái xảy ra:

Qn

0

0

0

0

1

1

1

1

R

0

0

1

1

0

0

1

1

S

0

1

0

1

0

1

0

1

Qn+1

0

1

0

x

1

1

0

x

Phương trình đặc trưng của FF:

Q

Q

Bảng Karnaugh:

Q

RS 00

n

0

0

01

A

1

1

1

1

S

11

x

10

B

0

x

0

R

Q n +1 = S + RQ n

RS = 0 (ràng buộc từ trạng th¸i cÊm)

.

2. Flip flop RS đồng bộ

2.1 Cấu trúc mạch và ký hiệu:

Q

Q

Để khắc phục nhược điểm của

FF RS cơ bản là trực tiếp điều

khiển, người ta thêm vào hai cổng

A

B

điều khiển và một tín hiệu điều

Q

Q

khiển, nên tín hiệu đầu vào được

truyền qua cổng điều khiển. Các

C

D

cổng A, B làm thành FF RS cơ

R CP S

bản, các cổng C, D là cổng điều

CP

R

S

khiển, CP là tín hiệu điều khiển,

thường là xung đồng hồ hoặc xung

mở chọn mạch.

2.2 Nguyên lý làm việc:

Khi CP = 0, các cổng C, D bị ngắt, FF bị cấm, duy trì trạng thái cũ.

Khi CP = 1, các cổng C, D thông thì FF sẵn sàng (tiếp thu tín hiệu),

nó tiếp thu tín hiệu đầu vào R, S. Ta thấy rằng, hoạt động của mạch

lúc này hoàn toàn giống như FF RS cơ bản.

+ R = 0, S = 1: đầu ra cổng C ở mức thấp, FF

lật ở trạng thái 1.

Q

Q

A

B

+ R = 1, S = 0: đầu ra cổng D ở mức thấp, FF bị

xóa về trạng thái 0.

+ R = S = 0: các cổng C, D đều đưa ra mức cao,

FF sẽ duy trì trạng thái cũ.

+ R = S = 1: thì các cổng C, D đều đưa ra mức

thấp, dẫn đến Q và Q đều là mức cao, đó là

C

S

D

CP

R

trạng thái cấm.

Do đó, bảng chức năng và phương trình đặc trưng biểu thị quan hệ

logic giữa Qn+1 và Qn, R, S gần giống như FF RS cơ bản, chỉ khác

là thêm trong điều kiện CP = 1.

2.3 Mạch chốt D:

Q

A

Được cấu tạo trên cơ sở mạch FF RS đồng bộ

nhằm giải quyết vấn đề ràng buộc lẫn nhau của

các tín hiệu đầu vào R, S. Đầu ra cổng C nối

đến các đầu vào cổng A, E.

C

Q

B

E

Khi CP = 0: cổng C, E ngắt nên FF duy trì

trạng thái cũ.

D

CP

Khi CP = 1:

+ D = 0: C = 1, E = 0 FF ở trạng thái 0.

+ D = 1: C = 0, E = 1 FF ở trạng thái 1.

Vậy phương trình đặc trưng của mạch chốt FF D là:

Qn+1 = D với điều kiện: CP = 1.

2.4 Đặc điểm cơ bản của FF RS đồng bộ:

ã Ưu điểm: Điều khiển chọn mở mạch.

ã Nhược điểm: Trong thời gian CP = 1, tín hiệu vào vẫn trực tiếp

điều khiển trạng thái đầu ra của FF.

.

Q

3. Flip flop RS chđ tí (Master - Slave)

Q

3.1 CÊu trúc mạch và ký hiệu:

B

A

3.2 Nguyên lý làm việc:

Hai FF RS đồng bộ nối ghép dây

-chuyền với 0:

Khi CP = nhau, một là FF master,

Slave

C

D

một là FF slave, xung đồng hồ cung

Cổng G, H ngắt nên FF master ngắt.

cấp cho chúng là đảo nhau.

Qm

CP = 1 , cổng C, D thông nên FF slave

Qm

sẵn sàng, nó tiếp thu tín hiệu ®Çu ra

E

F

I

Q = Q m.

master, do ®ã: Q = Qm,

Master

G

H

- Sau khi đột biến sườn dương CP:

CP = 1 master thông qua các cổng G,

CP

S

R

H tiếp nhận tín hiệu đầu vµo.

VËy: Q n +1 = S + RQ n

m

m

Q Q

Víi ®iỊu kiƯn: CP = 1

RS = 0

CP = 0 slave bị ngắt, đầu ra Q, duy trì trạng thái cũ.

S CP R

- Khi sườn âm xung đồng hồ CP:

CP đột biến xuống 0, master bị ngắt.

CP đột biến lên 1, slave tiếp nhận tín

hiệu đà được master ghi nhớ từ thời

gian CP = 1, nghĩa là slave chuyển đổi

trạng thái.

Vậy: Q n +1 = S + RQ n

RS = 0

Víi ®iỊu kiện đà xuất hiện sườn

âm của CP.

Q

Q

A

B

C

Slave

Qm

Qm

E

G

D

F

Master

I

H

CP

3.3 Đặc điểm cơ bản:

S

R

ã Ưu điểm: Cấu trúc điều khiển master slave đà giải quyết vấn đề

trực tiếp điều khiển, trong khi CP = 1 tiÕp thu tÝn hiƯu, sên ©m

cđa CP kÝch chuyển trạng thái đầu ra.

ã Nhược điểm: Vẫn còn ràng buộc giữa R và S khi CP = 1.

4. Flip flop JK chđ tí (Master - Slave)

4.1 CÊu trúc mạch và ký hiệu:

FF RS master slave nói ở trên vẫn

còn ràng buộc R và S, nguyên nhân

chính là khi R = S = 1 đầu ra các cổng

G, H đều ở mức thấp, dẫn đến tình

huống không mong muốn là Qm = 1 và

Qm = 1

Xét mạch FF RS master slave khi CP

= 1, Q và Q không đổi trạng thái và là

đảo của nhau. Chỉ cần đem mức các đầu

ra Q và Q đưa đến đầu vào của G, H thì

có thể khắc phục tình trạng cả Qm = 1

và Q m = 1 giải quyết vấn đề ràng buộc

.

Q

Q

A

B

C

Slave

D

Qm

Qm

E

G

J

F

Master

H

CP

Q

K

Q

giữa tín hiệu đầu vào.

J CP K

I

4.2 Nguyên lý làm việc:

Đây là mạch cải tiến của mạch FF

RS master slave nên nguyên lý làm việc

giống như FF RS master slave, chỉ khác

bởi sự tương đương sau của các tín hiệu

đầu vào:

n

S = JQ

R = KQ n

Q

Q

A

B

C

Qm

E

Slave

D

Qm

F

I

Vậy:

n

n +1

n

Q = S + RQ = J Q + KQ n Q n

Master

G

H

n

n

= J Q + KQ

Víi ®iỊu kiƯn ®· xuất hiện sườn âm

CP

J

K

xung đồng hồ CP.

4.3 Đặc điểm cơ bản:

ã Ưu điểm: J và K không bị ràng buộc lẫn nhau, các IC của chúng

được sản xuất nhiều, sử dụng rộng rÃi, tính năng ưu việt.

ã Nhược điểm: Yêu cầu J, K duy trì không đổi trong thời gian CP = 1.

.

5. Flip flop D

5.1 Cấu trúc mạch điện:

Q

Q

A

B

5.2 Nguyên lý làm việc:

Z1

Z2

- Khi CP = 0:

Các cổng C, D bị khóa, Z1 = Z2 = 1,

C

D

FF cơ bản gồm các cổng A, B duy trì

CP

Z3

trạng thái cũ.

Z4

F

E

+ Nếu D = 1 th×: Z 4 = D ⋅ Z 2 = 1⋅1 = 0

Z3 = Z1 ⋅ Z 4 = 1⋅ 0 = 1

D

CP đóng vai trò tín hiệu đầu vào đối với cổng C

thông, cổng D ngắt.

+ Nếu D = 0 th×: Z 4 = D ⋅ Z 2 = 0 ⋅1 = 1

Z3 = Z1 ⋅ Z 4 = 1 1 = 0

CP đóng vai trò tín hiệu đầu vào đối với cổng C ngắt, cổng D

thông.

- Thêi gian sên d¬ng cđa CP:

+ NÕu D = 1 thì D bị ngắt, CP chỉ có thể

thông qua cæng C më.

Z1 = Z3 ⋅ CP = 1⋅1 = 0

Z1 = 0 dẫn đến 3 tác động sau:

- Kích FF thiÕt lËp 1: Q = 1, Q = 0.

- Ngăn trở trạng thái 0 của FF.

CP

- Duy trì trạng thái 1 của FF.

+ Nếu D = 0 thì C bị ngắt, CP chỉ có thể

thông qua cổng D mở.

Z 2 = Z1 ⋅ Z 4 ⋅ CP = 1 11 = 0

Z2 = 0 dẫn đến 2 tác động sau:

Q

Q

A

B

Z1

Z2

C

D

Z3

E

F

Z4

D

- Xãa FF vÒ 0: Q = 0, Q = 1 .

- Duy trì trạng thái 0 của FF.

Tóm lại:

Qn+1 = D với điều kiện đà xuất hiện sườn dương cña CP.

5.3 Đặc điểm cơ bản:

ã Ưu điểm: Điều khiển sườn xung, kÝch víi sên d¬ng CP,

trong thêi gian CP = 1 mạch tự giữ nguyên trạng.

ã Nhược điểm: Trong một số trường hợp, sử dụng không tiện

bằng FF JK.