Chöông 3 giới thiệu về PIC 16f877a

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (1.12 MB, 16 trang )

Chương 3:Giới thiệu về PIC 16f877a

3.1Đây là vi điều khiển thuộc họ PIC16Fxxx với tập

lệnh gồm 35 lệnh có độ dài 14 bit. Mỗi lệnh đều

được thực thi trong một chu kì xung clock. Tốc độ hoạt

động tối đa cho phép là 20 MHz với một chu kì lệnh là

200ns. Bộ nhớ chương trình 8Kx14 bit, bộ nhớ dữ liệu

368x8

byte RAM và bộ nhớ dữ liệu EEPROM với dung lượng

256x8 byte. Số PORT I/O là 5 với 33 pin I/O.

Các đặc tính ngoại vi bao gồm các khối chức

năng sau:

Timer0: bộ đếm 8 bit với bộ chia tần số 8 bit.

Timer1: bộ đếm 16 bit với bộ chia tần số, có

thể thực hiện chức năng đếm dựa vào xung clock

ngoại vi ngay khi vi điều khiển hoạt động ở chế

độ sleep.

Timer2: bộ đếm 8 bit với bộ chia tần số, bộ

postcaler.

Hai bộ Capture/so sánh/điều chế độ rông xung.

3.2 Sô ñoà chaân vi ñieàu khieån PIC

2

3

4

5

6

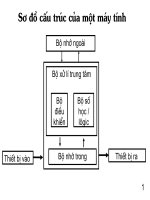

3.3 TỔ CHỨC BỘ NHỚ

Cấu trúc bộ nhớ của vi điều khiển PIC16F877A

bao gồm bộ nhớ chương trình (Program memory) và bộ

nhớ dữ liệu (Data Memory).

3.3.1.BỘ NHỚ CHƯƠNG TRÌNH

Bộ nhớ chương trình của vi

điều khiển

PIC16F877A là bộ nhớ flash, dung

lượng bộ

nhớ 8K word (1 word = 14 bit) và

được phân thành nhiều trang (từ

page0 đến page 3) .Như vậy bộ

nhớ chương trình có khả năng

chứa được 8*1024 = 8192 lệnh (vì

một lệnh sau khi mã hóa sẽ có

dung lượng 1 word (14 bit).Để mã

hóa được đòa chỉ của 8K word

bộ nhớ chương trình, bộ đếm

chương trình có dung lượng 13 bit

(PC<12:0>).Khi vi điều khiển được

reset, bộ đếm chương trình sẽ

chỉ đến đòa chỉ 0000h (Reset

vector). Khi có ngắt xảy ra, bộ

đếm chương trình sẽ chỉ đến đòa chỉ 0004h (Interrupt

vector).Bộ nhớ chương trình không bao gồm:Bộ nhớ

stack và không được đòa chỉ hóa bởi bộ đếm chương

trình. Bộ nhớ stack sẽ được đề cập cụ thể trong phần

sau.

7

3.3.2 BỘ NHỚ DỮ LIỆU

Bộ nhớ dữ liệu của PIC là bộ nhớ EEPROM được

chia ra làm nhiều bank. Đối với PIC16F877A bộ nhớ dữ

liệu được chia ra làm 4 bank. Mỗi bank có dung lượng 128

byte, bao gồm các thanh ghi có chức năng đặc biệt SFG

(Special Function Register) nằm ở các vùng đòa chỉ thấp

và các thanh ghi mục đích chung GPR (General Purpose

Register) nằm ở vùng đòa chỉ còn lại trong bank. Các

thanh ghi SFR thường xuyên được sử dụng (ví dụ như

thanh ghi STATUS) sẽ được đặt ở tất cà các bank của

bộ nhớ dữ liệu giúp thuận tiện trong quá trình truy

xuất và làm giảm bớt lệnh của chương trình. Sơ đồ

cụ thể của bộ nhớ dữ liệu PIC16F877A như sau:

8

I – Các port của PIC16F87X

9

* PORTA và thanh ghi TRISA

PORTA có độ rộng 6 bit , là port vào ra hai chiều .Thanh ghi dữ

liệu trực tiếptương ứng là TRISA . Cho tất cảa các bit của TRISA là

1 thì các chân tương ứng ởPORTA là ngõ vào. Cho tất cả các bit

của TRISA là 0 thì các chân tương ứng ở PORTA là ngõ ra .Việc đọc

các thanh ghi của PORTA sẽ đọc trạng thái của những chân ,

ngược lại việc ghi lên nó sẽ ghi qua port chốt . Tất cả những hoạt

động ghi là các hoạt động đọc-điều chỉnh-ghi . Bởi vậy , dữ liệu

được ghi đến port có nghĩa là những chân của port là đọc , giá trị

được chỉnh sửa và được ghi vào port chốt dữ liệu .Chân RA4 được

đa hợp với xung clock ngoài ở ngõ vào của Timer0 thành

chânRA4/T0CKI . Chân RA4/T0CKI là ngõ vào có một Trigger

Schmitt và một ngõ ra códạng thoát mở . Tất cả những chân khác

của PORTA có ngõ vào TTL và có ngõ ra điều khiển CMOS .Những

chân khác của PORTA được đa hợp với ngõ vào tương tự và ngõ

vàotương tự VREF . Hoạt động của mỗi chân được chọn bằng cách

xoá hoặc đặt những bit điều khiển trong thanh ghi ADCON1 ( A/D

Control Register1 ).Thanh ghi TRISA điều khiển hướng của những

chân RA , ngay cả khi chúng được sử dụng như ngõ vào tương

tự .Người sử dụng cần phải chắc rằng những bit trong thanh ghi

TRISA luôn luôn được đặt khi sử dụng chúng như ngõ vào tương

tự .

* PORTB và thanh ghi TRISB

PORTB có độ rộng 8 bit , là port vào ra hai chiều . Ba chân của

PORTB được đahợp với chức năng lập trình mức điện thế thấp

(Low Voltage Programming ) :RB3/PGM , RB6/PGC và RB7/PGD .

Mỗi chân của PORTB có một điện trở kéo lên yếu ở bên trong .

Một bit điều khiển đơn có thể mở tất cả những điện trở kéo lên

10

này .Điều này được thực hiện bằng cách xóa bit RBPU

(OPTION_REG<7>) . Những điệntrở kéo lên này sẽ tự động tắt khi

các chân của port được cấu hình như ngõ ra . Các điện trở này bị

cấm khi có một Power-on Reset . Bốn chân của PORTB ,

RB7:RB4 ,có một ngắt để thay đổi đặc tính . Chỉ những chân được

cấu hình như ngõ vào mới có thể gây ra ngắt này . Những chân

vào RB7:RB4 ) được so sánh với giá trị được chốt trước đó trong

lần đọc cuối cùng của PORTB .Các kết quả không phù hợp ở ngõ

ra trên chân RB7: RB4 được OR với nhau để phát ra một ngắt Port

Change RB với cờ ngắt là RBIF ( INTCON<0> ) . Ngắt này có thể

đánh thức thiết bị từ trạng thái nghĩ( SLEEP ) . Trong thủ tục phục

vụ ngắt , người sử dụng có thể xóa ngắt theo cách sau

a) Đọc hoặc ghi bất kì lên PORTB . Điều này sẽ kết thúc điều kiện

không hòa hợp .

b)XóabitcờRBIF

*PORTC và thanh ghi TRISC

PORTC có độ rộng là 8 bit , là port hai chiều . Thanh ghi dữ liệu

trực tiếp tương ứng là TRISC . Cho tất cả các bit của TRISC là 1 thì

các chân tương ứng ở PORTC là ngõ vào . Cho tất cả các bit của

TRISC là 0 thì các chân tương ứng ở PORTC là ngõ ra . PORTC được

đa hợp với vài chức năng ngoại vi , những chân của PORTC có

đệmTrigger Schmitt ở ngõ vào . Khi bộ I2C được cho phép , chân 3

11

và 4 của PORTC cóthể được cấu hình với mức I2C bình thường ,

hoặc với mức SMBus bằng cách sử dụng bit CKE (SSPSTAT<6>) .

Khi những chức năng ngoại vi được cho phép , chúng tacần phải

quan tâm đến việc định nghĩa các bit của TRIS cho mỗi chân của

PORTC .Một vài thiết bị ngoại vi ghi đè lên bit TRIS để tạo nên một

chân ở ngõ ra , trong khi những thiết bị ngoại vi khác ghi đè lên

bit TRIS thì sẽ tạo nên một chân ở ngõ vào .Khi những bit TRIS ghi

đè bị tác động trong khi thiết bị ngoại vi được cho phép ,những

lệnh đọc-thay thế-ghi ( BSF , BCF , XORWF ) với TRISC là nơi đến

cần phải được tránh . Người sử dụng cần phải chỉ ra vùng ngoại vi

tương ứng để đảm bảo choviệc đặt TRIS bit là đúng

12

13

*PORTD và thanh ghi TRISD

PORTD và TRISD không có đối với PIC16F873 hoặc PIC16F876 .

PORTD là port 8 bit với đệm Trigger Schmitt ở ngõ vào . Mỗi chân

có thể được cấu hình riêng lẻ như một ngõ vào hoặc ngõ

ra.PORTD có thể được cấu hình như port của bộ vi xử lýrộng 8 bit

( parallel slave port ) bằng cách đặt bit điều khiển PSPMIDE

( TRISE <4>).

Trong chế độ này , đệm ở ngõ vào là TTL .

PORTE và thanh ghi TRISE

PORTE và TRISE không có đối với PIC16F873 hoặc PIC16F876 .

PORTE có ba chân (RE0/RD/AN5 , RE1/WR/AN6 , và RE2/CS/AN7 )

mỗi chân được cấu hình riêng lẻ như những ngõ vào hoặc những

ngõ ra . Những chân này có đệm TriggerSchmitt ở ngõ vào .

Những chân của PORTE đóng vai trò như những ngõ vào điều

khiển vào ra cho port của vi xử lý khi bit PSPMODE ( TRISE <4> )

được set .Trong chế độ này , người sử dụng cần phải chắc rằng

những bit TRISE <2:0> được set , và chắc rằng những chân này

được cấu hình như những ngõ vào số . Cũng bảo đảm

rằngADCON1 được cấu hình cho vào ra số . Trong chế độ này ,

những đệm ở ngõ vào làTTL .Những chân của PORTE được đa hợp

với những ngõ vào tương tự . Khi được chọn cho ngõ vào tương

tự , những chân này sẽ đọc giá trị ‘0’ TRISE điều khiểnhướng của

những chân RE chỉ khi những chân này được sử dụng như những

ngõ vào tương tự . Người sử dụng cần phải giữ những chân được

14

cấu hình như những ngõ vào khi sử dụng chúng như những ngõ

vào tương tự .

3.3.4 – Bộ nhớ dữ liệu EEPROM và bộ nhớ chương trình

FLASH

Bộ nhớ dữ liệu EEPROM và bộ nhớ chương trình FLASH cho phép

đọc hoặc ghi trong suốt hoạt động bình thường trong phạm vi

VDD . Những thao tác này xảy ra trên một byte đơn cho bộ nhớ

dữ liệu EEPROM và trên một từ đơn cho bộ nhớ chương

trìnhFLASH . Một thao tác ghi gây ra sự xóa rồi ghi , thao tác này

được thực hiện trên mộtbyte hoặc một từ được chỉ định . Sự truy

cập vào bộ nhớ chương trình phải kể đến sự tính toán

checksum .Ghi một byte hoặc một word sẽ tự động xóa vùng nhớ

và ghi lên giá trị mới ( xóatrước khi ghi ) . Việc ghi vào bộ nhớ dữ

liệu EEPROM không ảnh hưởng đến hoạt độngcủa thiết bị . Việc

ghi vào bộ nhớ chương trình sẽ dừng thực thi các lệnh cho đến khi

quátrình ghi hoàn thành . Bộ nhớ chương trình không thể được

truy cập trong suốt quátrìnhghi. Trong suốt quá trình ghi , bộ dao

động tiếp tục chạy , thiết bị ngoại vi vẫn tiếp tục hoạt động và

những sự kiện về ngắt sẽ được phát hiện và đợi cho đến khi quá

trình ghi hoàn thành . Khi quá trình ghi hoàn thành , lệnh tiếp

theo trong hàng đợi lệnh sẽ được thực hiện và một rẽ nhánh đến

vectơ ngắt sẽ xảy ra đến ngắt được phép và gây ra trong suốt

quá trình ghi .Việc đọc và ghi truy cập đến cả hai bộ nhớ xảy ra

giántiếp thông qua việc đặt những thanh ghi mục đích chung

( SFR ) . Có sáu thanh ghi mục đích chung được sử dụng là

EEDATA

EEDATH

EEADR

EEADRH

EECON1

EECON2

Bộ nhớ dữ liệu EEPROM cho phép những thao tác đọc và ghi byte

không can thiệp đến những thao tác bình thường của bộ vi điều

khiển . Khi có sự trao đổi với bộ nhớ dữ liệu EEPROM , thanh ghi

EEADR giữ địa chỉ sẽ được truy cập .Phụ thuộc vào thao tác

,thanh ghi EEDATA giữ dữ liệu được ghi hoặc được đọc tại địa chỉ

trong thanh ghiEEADR . PIC16F873/874 có 128 byte cho bộ nhớ

dữ liệu EEPROM . PIC16F876/877 có 256 byte cho bộ nhớ dữ liệu

EEPROM và do đó nó sử dụng tất cả 8 bit của EEADR

15

3.3.5 – Quá trình đọc bộ nhớ dữ liệu EEPROM

Quá trình đọc bộ nhớ dữ liệu EEPROM chỉ yêu cầu địa chỉ cần truy

cập phải được ghi vào thanh ghi EEADR và xóa bit EEPGD . Sau

khi bit RD được set , dữ liệu sẽ phải sẵnsàng trong thanh ghi

EEDATA trong chu kỳ lệnh kế tiếp . EEDATA sẽ giữ giá trị nàycho

đến khi thao tác đọc kế tiếp được bắt đầu hoặc cho đến khi nó

được ghi bởi vi chương trình .

Các bước trong quá trình đọc bộ nhớ dữ liệu EEPROM là :

1. Ghi địa chỉ cần truy cập vào thanh ghi EEADR và hãy chắc rằng

địa chỉ này thì không lớn hơn kích thước bộ nhớ của linh kiện

PIC16F87X .

2. Xóa bit EEPGD để trỏ đến bộ nhớ dữ liệu EEPROM.

3. Set bit RD để bắt đầu thao tác đọc.

4. Đọc dữ liệu từ thanh ghi EEDATA:

Quá trình ghi dữ liệu vào bộ nhớ dữ liệu EEPROM được tiến hành

qua vài bước . Cả địa chỉ và giá trị dữ liệu cần phải được ghi vào

những thanh ghi mục đích chung SFR .Bit EEPGD cần phải được

xóa , và bit WREN phải được set để cho phép ghi . Bit WREN phaỉ

bị xóa trong suốt thời gian ngoại trừ trong quá trình ghi vào bộ

nhớ dữ liệuEEPROM . Bit WR chỉ có thể được set khi bit WREN đã

được set.

16