Bài giảng Kỹ thuật số - Phần 10: Mạch đăng ký di chuyển

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (357.38 KB, 13 trang )

MẠCH ĐĂNG KÝ DI CHUYỂN

(SHIFT REGISTER)

I. Đại cương

Mỗi flipflop có 2 trạng thái 0 hay

1 và ta có thể kích thích vào

một trong hai trạng thái đó như

ý muốn. Các ngõ ra chỉ thay

đổi khi ta bắt buộc thay đổi. Ta

nói flipflop có đặc tính ký ức.

Nếu ta dùng nhiều flipflop ta có

thể ghi vào chuỗi số nhò phân n

Nhóm FF dùng vào công việc

này để thành lập mạch đăng

ký. Thường các FF không nằm

cô lập mà được nối với nhau

theo một kiểu cách nào đó, sao

cho có thể truyền dữ liệu cho

nhau. Nhóm FF dùng vào việc

điều khiển này thành lập mạch

1 di

0 chuyển.

1 1 n bit

đăng ký

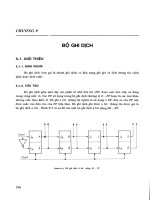

II. Dữ liệu vào theo lối nối tiếp

Ta dùng 4 FF dưới dạng FF-D được

mắc như ở hình vẽ.

CL

CK

Q

9

D

Q

CLR

D

QD

QC

CLK

9

CLR

Q

CLR

D

CLR

Q

CLK

D

CLK

Va

øo

nố

i

tie

áp

QB

CLK

QA

Ra song song

Ra

nố

i

tie

áp

Đầu tiên ta có 4 FF bằng 0 ( nối

clear xuống mass) ta tuần tự cho

dữ liệu ở ngõ vào nối tiếp. Khi

có một cạnh lên của xung CK dữ

liệu đi vào trong mạch đăng ký di

chuyển 1 bit, với dữ liệu n bit thì

sau n xung CK dữ liệu nằm hoàn

toàn trong mạch đăng ký di

chuyển.

Lúc đó ta có thể lấy ra theo lối

song

song bằng

cách lấy các ngõ

DL

vaøo

CK

QA

QB

QC

QD

0

1

0

1

1

1

1

1

1

0

0

1

0

1

1

1

1

1

0

0

0

1

0

1

1

1

1

0

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

1

J

CK

FF J-K

K

Pr Cl

Clock

74LS00

Điều

khiể

n

nhậ

n

vào

QC

CK

FF J-K

K

FF J-K

Pr Cl

C = 1

&

Pr Cl

QB

1

74LS04

J

1

&

&

K

QC

B = 0

QA

QB

&

CK

A = 1

J

QA

QB

&

QA

1

&

III. Dữ liệu vào theo lối song

song

Song song

Vào song song

Ra

nối

tiếp

Muốn cho dữ liệu vào theo lối

song song, ta phải đặt sẵn dữ

liệu tại các ngõ A, B, C. Khi

ngõ điều khiển nhận vào lên 1 ta

thấy:

Nếu A = 1 nên Q = 1.

A

Nếu B = 0 nên QB = 0. Ta nói dữ

liệu từ ngõ vào được đưa đến

ngõ ra khi ngõ điều khiển nhận

vào lên 1.

Ngõ đồng

hồ CK không có tác

Muốn ngõ ra theo lối nối tiếp, ta lấy ở

ngõ cuối cùng.

Muốn mạch dòch trái, ta phải nối các

đường hồi tiếp QC về ngõ vào B, QB về

ngõ vào A và ngõ ra QA chính là ngõ ra nối

tiếp, ngõ vào nối tiếp chính là ngõ vào C.

Khi lấy ra theo nối tiếp thì dữ liệu sẽ bò

mất đi. Muốn dữ liệu không bò mất, ta nối

đường hồi tiếp từ ngõ ra cuối cùng trở về

ngõ vào đầu.

Ta cần thêm 1 số cổng logic để thiết kế dữ

liệu vào theo lối nối tiếp, thiết kế dữ liệu

vào và ra theo lối song song, hoặc dữ liệu ra

Và

o

nối

tiế

p

ĐK

Ra song song

MẠCH ĐKDC

Ra nối

tiếp

ĐK = 0: vào nối tiếp

ĐK = 1: hồi tiếp (chạy tuần

hoàn),

74164

Maùch

traựi:

dũch

Ra noỏi

tieỏp QA

S

QA

QB

S

Vaứo noỏi

tieỏp

QB

1

CK

CK

R

R

74LS04

CK

QB

Maùchdũchphaỷi:

QA

Vaứo

noỏi

tieỏp

S

1

74LS04

CK

S

CK

CK

R

QA

QB

QA

R

QB

Ra noỏi

tieỏp

Thí dụ:

7494 : 4 bit, vào // hay nối tiếp –

ra nối tiếp

7495 : 4 bit, vào // hay nối tiếp –

ra // hay dòch phải trái.

74164: 8 bit, vào // - ra nối tiếp

74194: 4 bit, vào // hay nối tiếp –

ra // , nạp đồng bộ, dòch

phải/trái.

IV. ỨNG DỤNG

Lưu

trữ

và

chuyển dữ liệu.

Tạo ký tự hay tạo

dạng điều khiển.

Chuyển đổi dữ

từ nối tiếp ra

dòch

các

liệu

song