Tài liệu ung dung PLD trong viec dieu khien dong co buoc pdf

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (64.99 KB, 13 trang )

ĐỒ ÁN 2

Chương 1 : Cơ Sở Lý Thuyết

I .Giới thiệu chung :

Trong một số hệ thống số ,việc sử dụng các mạch tính hộp số với vô số các hàm logic

cơ bản hay các IC chuẩn để tạo nên các ứng dụng cụ thể đã làm cho các nhà thiết kế

trở nên linh hoạt hơn và việc thiết kế cũng trở nên dễ dàng hơn .Tuy nhiên với những

thiết kế lớn đòi hỏi hàng trăm đến hàng ngàn IC chuẩn như vậy thì việc thiết kế sẽ gặp

phải những khó khăn mà nhà thiết kế phải đối mặt như :khoảng không gian đáng kể

trên mạch ,quá trình lắp ráp và thi công sẽ phức tạp ,dò tìm cũng khó

khăn ,khả năng và độ tin cậy của việc thiết kế cũng giảm đi …Để giải quyết

những vấn đề này , nhà thiết kế cần phải giảm bớt số IC và tích hợp các chức năng

logic trên một chip càng nhiều càng tốt .Để làm được điều này thì việc sử dụng thiết bò

logic lập trình được (Progrmmable Logic Device)là điều mà các nhà thiết kế cần phải

nghó đến.

PLD là IC chứa rất nhiều cổng ,FF ,thanh ghi ,được nối với nhau trên chip.Tuy

nhiên nhiều mối nối trong số đó là mối nối chì ,vì vậy có thể đốt đứt chúng .IC này sở

dó được g là cho phép lập trình vì chức năng cụ thể của IC ở một ứng dụng cụ thể

được quyết đònh bằng cách đốt đứt một số mối nối chọn lọc trong lúc giũ nguyên số mối

nối còn l .Quá trình đốt đứt cầu chì có thể do nhà sản xuất thực hiện theo yêu cầu của

khàch hàng hoặc do chính khách hàng thực hiện .Quá trình này gọi là lập trình .Vì kết

quả tạo thành là mẫu hình mạch mong muốn nối kết các cổng ,FF và thanh ghi…

II .Các ưu điểm của PLD trong thiết kế :

- Tăng khả năng tích hợp :Có thể giảm khối lượng về mạch thiết kếtrong khi vẫn có

thể tăng chức năngcho mạch .

- Công suất thấp : MOS và một số ít hơn các mạch kết hợp sẽ làm giảm đáng kể

công suất nguồn cung cấp.

- Tăng độ tin cậy : Nguồn cung cấp thấp và và việc giảm tối đa các mạch liên kết ở

ngoài làm cho việc truyền giửa các khối đáng tin cậy hơn .

- Giá thành thấp .

- Dễ sử dụng .

-Dễ dàng thay đổi : Khi cần có sự thay đổi trong thiết kế ,không cần phải thêm các

dây nối , tất cả là thay đổi bên trong của PLD và có thể thực hiện các thay đổi đó một

cách nhanh chóng nhờ khả năng có thể lập trình của nó .

* Một số dạng PLD thông dụng :

PLD là thiết bò bộ nhớ hàm , ta có thể kê ra các loại linh kiện liên quan đến PLD

theo sơ đồ sau :

PLA PAL LCA EPLD PEEL GAL

PPAL

EPPAL

EEPPAL

PLD :Programmable Logic Device.

PLA : Programmable Logic Array.

PAL : Programmable Array Logic .

LCA :Logic Cell Array .

EP :Erasable and Programmable.

EEP : Electrically Erasable and Programmable .

PEEL:Programmable Electrically Erasable Logic .

GAL : Generic Array Logic .

III. Cấu trúc của một số loại PLD :

1 .Mảng Logic lậptrình được (PLA):

Một PLA vơi n ngỏ vào và n ngỏ ra có thể cài đặt n hàm của n biến ,tổ chức nội

của PLA như sau :

Hai dãy AND và OR có thể được lập trình để thực hiện bất cứ biểu thức logic tích

chuẩn nào phù hợp với số ngỏ vào và ngỏ ra của thiết bò .

BỘ NHỚ HÀM

PLD

2. Logic mảng lập trình được (PAL)

PAL là trường hợp đặc biệt của PLA ,ở đó các dãy AND là lập trình được và dãy OR

là cố đònh .

Cấu trúc cơ bản củ PAL :

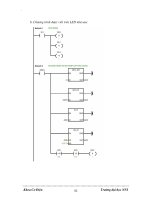

3. PLD tuần tự :

Phần lớn các thiết kế số lần các FF ,do đó người ta đưa ra thêm các PLD có chứa các

FF các PLD như vậy thường được gọi là PLD có thanh ghi hay PLD tuần tự .

Cấu trúc cơ bản của một đoạn PLD tuần tự :

4. Một số PLD khác :

-Mảng logic cho phép lập trình trong (FPLA)là thiết bò logic không nhớ đầu tiên cho

phép lập trình FPLA sử dụng mảng cổng AND cũng như mảng cổng OR cho phép lập

trình . Mặc dù cấu trúc FPLA linh động hơn PAL nhưng nó vẫn không được giới kỹ sư

chấp nhận rộng rãi.

-PLD phức (CPLD), còn gọi là mảng đa cấp ,là loại linh kiện kết hợp một số sơ đồ

dạng mạch kiểu PAL trên cùng chip .Bản thân các khối logic là cổng AND lập trình

được , cổng OR cố đònh với it1 số hạng tích hơn cấu trúc PAL Khi cần nhiều số hạng

tích hơn ,một mảng cổng NAND được nối thêm làm số hạng đầu vào ,hoặc kết hợp

thêm nhiều khối logic hẫu ứng dụng biểu thức .

- Mảng cổng cho phép lập trình trong (FPGA)đưa ra một số khối logic đònh cấu hình

được ,có chứa logic tổ hợp lập trình được và thanh ghi cho mạch tuần tự .Còn có tập hợp

các khối vào /ra được lập cấu hình như đầu vào cố đònh đầu ra cố đònh hay hai chiều

.Đầu ra có khả năng ba trạng thái ,thanh ghi dùng để chất dữ liệu vào hay ra .Mọi khối

logic có thể lập và các khối vào / ra đều cho phép liên kết bằng cách lập trình nhằm

xây dựng gần như bất kỳ mạch logic nào .

5. PLD có thể xóa được .

Các PLD mà chúng ta đã đề cập đến được lập trình bằng cách nung đứt các mối chì.

Một khi các nối chì đã đứt ,chúng không còn nối l được . Vì vậy ,nếu phạm lỗi khi

đang lập trình ,hoặc muốn thay đổi kiểu thiết kế chỉ còn cách là bỏ linh kiện đó và

dùng linh kiện mới . Nhược điểmnày được khắc phục khi các nhà sản xuất tung ra loại

PLD có thể xóa và lập trình lại nhiều lần và được gọi là thiết bò logic cho phép xóa và

lập trình lại (Erasable Programmable Logic Device –EPLD).Trong PLD xóa được ,thay

cho mối nối chì là các chuyển mạch điện tử .Vì vậy trạng thái của chúng (đóng /mở)có

thể thay đổi bằng điện nhiều lần .

IV . PLD tuần tự loại GAL (Generic Array Logic)

1 . GAL 16 V8A:

Cấu trúc của GAL 16 V8A rất giống với cấu trúc của thiết bò PAL .Vì vậy ,có thể

dùng GAL 16 V8A như thiết bò tương thích thay thế cho hầu hết thiết bò PAL .

Thiết bò GAL sử dụng mảng EEPROM để chọn các số hạng đầu vào một số vò trí

nhất đònh trong mảng nhớ được chỉ đònh để kiểm soát các nối kết lập trình được cho ma

trận số hạng đầu vào .Mỗi bit trong ma trận số hạng đầu vào biểu diễn một mối nối lập

trình được giửa một hàng và một cột .Điều này cho phép xóa và lập trình lại thiết bò .

Các thành phần chính của thiết bò GAL là ma trận số hạng đầu vào ; cáccổng AND

tạo tích từ các số hạng đậu vào ;và các Macro logic đầu ra (Output logic Macro Cell –

OLMC).

Cấu trúc của một đoạn GAL 16 V8

2. Cấu trúc của GAL 16 V8Akhi hoạt động ở các chế độ

GAL 16V8A có 3 chế độ hoạt động khác nhau và ở mỗi chế độ có 1 cấu hình riêng .

-Chế độ đơn giản .

-Chế độ phức tạp .

-Chế độ thanh ghi .

a . Chế độ đơn giản (Simple mode).

Chế độ này thực hiện logic tổ hợp đơn giản mà không cần đầu ra 3 trạng thái .Đây là

cấu hình duy nhất có khả năng đưa 8 số hạng tích vào 1 biểu thức tổng để tạo đầu ra tổ

hợp .

Cấu hình ở Mode đơn giản

b. Chế độ phúc tạp (Complex mode).