BÁO cáo bài tập lớn vật lý bán dẫn đề tài tìm HIỂU về JFET

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (1 MB, 18 trang )

Ộ

GIÁO DỤC VÀ ĐÀO TẠ

ỜNG ĐẠI HỌC BÁCH K

ĐẠI HỌC QUỐC GIA TP.HCM

---o0o---

BÁO CÁO BÀI TẬP LỚN

VẬT LÝ BÁN DẪN

ĐỀ TÀI: TÌM HIỂU VỀ JFET

Giảng viên hướng dẫn: Phan Võ Kim Anh

ớp: L04

hóm: 12

1

DANH SÁCH THÀNH VIÊN:

STT

1

2

3

4

5

HỌ VÀ TÊN

Nguyễn Phạm Gia Phát (nh

Mai Trung Kiên

Nguyễn Xuân Bắc

Nguyễn Trọng Quí Dương

Cao Nguyễn Tiến Dũng

Đề tài: Tìm hiểu về JFET.

Yêu cầu: Cấu tạo, nguyên lý hoạt động, ứng dụng của JFET. So sánh JFET và MOSFET.

Phân tích 1 ví dụ về ứng dụng của JFET. (Proteus/ Lắp mạch).

DANH SÁCH PHÂN CHIA CÔNG VIỆC:

STT

1

2

3

4

5

2

MỤC LỤC

I.

GIỚI THIỆU VỀ JFET................................................................................................................. 4

II.

TÌM HIỂU VỀ JFET..................................................................................................................... 4

A. ĐẶC ĐIỂM............................................................................................................................... 4

B. CẤU TẠO.................................................................................................................................. 5

C. NGUYÊN LÝ HOẠT ĐỘNG.................................................................................................. 7

a. JFET kênh N....................................................................................................................... 7

b. JFET kênh P...................................................................................................................... 11

D. ỨNG DỤNG........................................................................................................................... 12

III. PHÂN TÍCH ỨNG DỤNG JFET VÀ MƠ PHỎNG BẰNG PROTEUS........................... 13

A. SỬ DỤNG JFET NHƯ MỘT CÔNG TẮC....................................................................... 13

B. CÁCH HOẠT ĐỘNG............................................................................................................ 14

a. Khi mở công tắc.............................................................................................................. 14

b. Khi đóng cơng tắc........................................................................................................... 14

c. Khi điện áp xả................................................................................................................. 15

C. MẠCH PROTEUS................................................................................................................. 16

IV. SO SÁNH JFET VÀ MOSFET.................................................................................................. 16

A. SO SÁNH JFET VÀ MOSFET............................................................................................ 16

B. ƯU VÀ NHƯỢC ĐIỂM....................................................................................................... 16

TÀI LIỆU THAM KHẢO..................................................................................................................... 18

3

I. GIỚI THIỆU VỀ JFET

-

FET (Field Effect Transistor - Transistor hiệu ứng trường) cũng là một trong các

dụng cụ điện tử quan trọng nhất trong công nghệ bán dẫn hiện đại. FET có 2 loại là JFET

và MOSFET.

-

Ở đây ta chỉ tập trung vào JFET-Transistor hiệu ứng trường chuyển tiếp cổng

(Junction Field Effect Transistor), được phát minh cùng thời điểm với Transitor nhưng tới

cuối năm 1960 mới được sử dụng rộng rãi, là loại đơn giản của transistor hiệu ứng trường.

II. TÌM HIỂU VỀ JFET

ĐẶC ĐIỂM

A.

-

JFET là Transistor hiệu ứng trường cổng nối (Junction Field Effect Transistor).

-

Nó là phần tử bán dẫn 3 chân, xây dựng dựa trên cấu trúc chuyển tiếp P-N.

4

CẤU TẠO VÀ KÝ HIỆU

B.

-

Cấu tạo: Trên một thanh bán dẫn hình trụ, người ta thiết kế đáy trên và đáy dưới lần

lượt tiếp xúc kim loại cho ra hai cực tương ứng là cực máng (DRAIN) và cực nguồn

(SOURCE). Tiếp đến, tạo một mối P – N vòng theo thanh bán dẫn. Kim loại tiếp xúc với

mẫu bán dẫn mới, đưa ra ngoài gọi là cực cổng (GATE). Miền bán dẫn giữa cực nguồn và

cực máng được gọi là kênh dẫn.

D (Drain): Cực máng (Cực thoát).

G (Gate): Cực cổng (Cực cửa).

S (Source): Cực nguồn.

-

Dựa vào cấu tạo của thanh bán dẫn hình trụ mà ta chia ra hai loại JFET:

5

JFET kênh N:

Cực D và cực S được kết nối vào kênh dẫn N.

Cực G được kết nối vào vật liệu bán dẫn P.

Ký hiệu:

JFET kênh P:

Cực D và cực S được kết nối vào kênh dẫn P.

Cực G được kết nối vào vật liệu bán dẫn N.

6

Ký hiệu:

NGUYÊN LÝ HOẠT ĐỘNG

C.

-

JFET hoạt động bằng cách giới hạn độ rộng kênh dẫn. Một ví dụ minh họa nguyên

lý hoạt động của JFET là cách hoạt động của vòi nước.

-

Tương tự với JFET, hiệu điện thế giữa cực cổng (Gate) và cực nguồn (Source) điều

chỉnh dòng điện chạy qua giữa cực nguồn (Source) và cực máng. Vậy chúng ta sẽ phân

tích một cách rõ ràng hơn nguyên lý hoạt động của JFET kênh N và kênh P (tức là xét về

mối quan hệ giữa VGS với VDS).

a. JFET kênh N

7

-

Đầu tiên, giả sử cực G và S nối với nhau và cực S nối đất, khi đó V GS = 0. Sau đó,

đặt một hiệu điện thế vào giữa cực D và cực S bằng một điện áp V DD (VDS > 0 tức là VD >

VS). Và lúc này electron di chuyển từ cực S → D theo kênh dẫn. Do đó, dịng điện có chiều

D → S. Bây giờ, ta sẽ xét hoạt động của JFET trong trường hợp này.

-

Khi nối mạch như vậy, VDS > 0 thì 2 chuyển tiếp P-N sẽ phân cực ngược và bề rộng

miền nghèo ở gần cực D rộng hơn miền nghèo ở gần cực S. Do trong quá trình hoạt động,

kênh N này hoạt động giống như một điện trở. Giả sử điện trở này đồng đều trong cả kênh

thì kênh N này có thể chia thành một chuỗi các điện trở giữa cực cổng và cực nguồn. Khi

có dịng điện ID chạy qua thì sẽ có sự sụt áp trên mỗi điện trở. Do đó vùng phía trên sẽ có

sự phân cực ngược lớn hơn so với vùng phía dưới dẫn đến sự chênh lệch độ rộng miền

nghèo. Khi tăng điện áp phân cực ngược thì độ rộng miền nghèo cũng tăng, do đó có một

lượng nhỏ dịng bão hịa ngược chạy qua chuyển tiếp P-N này nhưng khơng đáng kể và có

thể bỏ qua. Vì điều này mà trở kháng đầu vào của JFET rất cao.

-

Dưới đây là đồ thị ID theo VDS (khi ta tăng điện áp từ 0 đến vài vơn thì dịng điện

chạy trong kênh sẽ tăng lên).

8

-

Đường cong này cịn được gọi là đặc tính đầu ra của JFET. Đối với điện áp thấp thì

đồ thị gần như là một đường thẳng tuyến tính (khi điện áp thấp thì điện trở của kênh khơng

đổi). Nếu tiếp tục tăng điện áp V DS thì miền nghèo sẽ ngày càng rộng hơn và kênh N sẽ

ngày càng hẹp. Lúc này điện trở của kênh sẽ tăng lên và được thể hiện ở đồ thị trên khi

đường cong đi ngang hơn (tức là độ dốc giảm).

-

Khi điện áp tăng đến một mức nào đó và 2 miền nghèo sẽ chạm vào nhau, tình

trạng này gọi là nghẽn (pinch-off) và điện áp này cũng gọi là điện áp nghẽn (kí hiệu là Vp).

-

Vì vậy, bất cứ khi nào V DS ≥ Vp thì tình huống này sẽ xảy ra và JFET hoạt động ở

trạng thái bão hịa. Khi đó, có thể dịng điện sẽ khơng thể chạy qua kênh (I D = 0). Nhưng

thực tế, ID phải đạt đến trạng thái bão hịa chứ khơng thể bằng 0. Trước hết, ta giả sử rằng

9

khi điều này xảy ra thì ID = 0. Nếu trường hợp này xảy ra, thì điện áp phân cực sẽ khơng

cịn, dẫn tới miền nghèo sẽ biến mất. Dễ thấy điều này là vô lý và không thể xảy ra, do đó

ID khơng bằng 0 mà đạt đến dịng điện tối đa (kí hiệu là I DSS). Nếu trường hợp này xảy ra,

ID sẽ đạt đến giá trị tối đa (ký hiệu IDSS)

-

Nãy giờ ta chỉ xét trường hợp VGS = 0 nhưng VGS có thể kiểm sốt dịng điện trong

kênh và ảnh hưởng đến đặc tính đầu ra của JFET theo một cách nào đó. Vì vậy bây giờ ta

sẽ khảo sát giá trị của IDSS khi VGS càng âm.

-

Trước tiên ta giả sử VGS = -1V, sau đó tăng dần điện áp VDS từ 0V lên thì độ rộng

miền nghèo cũng tăng nhưng trạng thái pinch-off sẽ đạt được ở điện áp thấp hơn V DS. Đó

là do điện áp VGS âm này đã làm tăng độ phân cực ngược của chuyển tiếp P-N.

-

Vì vậy trong trường hợp VGS = -1V giá trị dòng điện bão hòa (IDSS) đã được giảm

như hình bên dưới.

10

-

Và giá trị của VGS càng âm thì IDSS càng giảm. Đến khi VGS = -Vp thì dịng diện bão

hịa sẽ bằng 0. Vùng hoạt động này của JFET được gọi là vùng tắt (cut -off).

-

Từ đó, ta thấy JFET có thể hoạt động trong 3 miền khác nhau là miền thuần trở

(ohmic), miền bão hòa (saturation) và miền tắt (cut-off). Trong miền ohmic JFET hoạt

động như một điện trở với giá trị cố định của V GS nó cung cấp một giá trị điện trở khơng

đổi do đó bằng cách thay đổi giá trị điện áp giữa cực cổng và cực nguồn ta có thể kiểm

sốt điện trở này. Tiếp theo là miền saturation, bất cứ khi nào V DS ≥ Vp thì ID sẽ gần như

khơng đổi. Cịn ở miền hoạt động thứ ba là cut-off, khi VGS ≤ -Vp thì ID sẽ xấp xỉ bằng 0.

-

Ngồi ra còn một miền hoạt động nữa của JFET là miền đánh thủng.

-

Trong miền bão hòa, nếu ta tăng V DS vượt quá một giới hạn nào đấy thì sẽ xảy ra

hiện tượng tăng vọt của dòng điện. Mức tối đa của VDS trong các JFET đều được xác

11

định, vì vậy phải đảm bảo giá trị của VDS khi hoạt động phải nhỏ hơn giá trị định mức này.

b. JFET kênh P

-

Đối với JFET kênh P cũng tương tự như JFET kênh N nhưng điện áp giữa cực

máng và cực nguồn phải âm (V DS < 0) và điện áp giữa cực cổng và cực nguồn phải dương

(VGS > 0). Khi đó dịng lỗ sẽ chạy từ cực nguồn sang cực máng qua kênh P.

-

Còn đồ thị biểu diễn điện áp ID theo VDS (hay đặc tính đầu ra của JFET) cũng tương

tự như JFET kênh N nhưng trong trường hợp này VDS này là âm.

12

-

Bây giờ ta tăng điện áp VGS (dương hơn) thì giá trị bão hòa của I D sẽ giảm. Và khi

VGS = Vp thì dịng điện sẽ xấp xỉ bằng 0. Cũng giống như JFET kênh N, khi điện áp V DS âm

hơn một giá trị định mức nào đó thì dịng điện cũng sẽ tăng mạnh.

ỨNG DỤNG

D.

-

Cơng dụng chung: Dùng làm khóa điện tử, bộ khuếch đại tín hiệu vi sai và kết hợp

các linh kiện điện tử khác trong hầu hết các thiết bị điện tử ngày nay: mạch kỹ thuật số,

máy tính, TV, máy thu thanh,…

Sử dụng như một cơng tắc điện tử để đóng ngắt mạch.

Bộ trộn âm: Dùng để khuếch đại âm thanh tần số thấp và hịa các tín hiệu âm thanh

để tạo ra các âm thanh khác nhau và nâng cao chất lượng âm thanh.

JFET là thiết bị có độ nhiễu rất thấp, nên khi được sử dụng ở đầu vào các thiết bị

thì chúng ta sẽ nhận được tín hiệu có độ nhiễu thấp hơn ở đầu ra.

Bộ khuếch đại đệm biến đổi trở kháng đầu vào cao thành trở kháng đầu ra thấp.

III.PHÂN TÍCH ỨNG DỤNG JFET VÀ MƠ

PHỎNG BẰNG PROTEUS

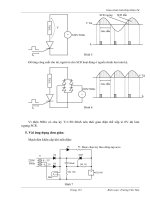

SỬ DỤNG JFET NHƯ MỘT CƠNG TẮC

A.

Để có cái nhìn trực quan hơn ta sẽ lấy mạch cơng tắc bóng đèn đơn

giản như sau:

-

-

Ta thay khóa K thành JFET (kênh N) như hình sau:

13

CÁCH HOẠT ĐỘNG

B.

a.

Khi cơng tắc mở:

-

Chúng ta có mạch cơng tắc như hình dưới. Với VGS = 0V, JFET kênh N sẽ cho phép

dòng điện chạy qua đèn nên đèn sẽ sáng.

b. Khi cơng tắc đóng:

-

Để tắt đèn, chúng ta cần kết nối một nguồn điện áp DC khác giữa các kết nối cổng

và nguồn của JFET. Đóng khóa K sẽ làm ngắt kênh của JFET, do đó buộc nó ở trạng thái

tắt (cut-off) và đèn sẽ tắt:

14

-

Mở lại công tắc điều khiển ta mong đợi sẽ ngắt điện áp DC ra khỏi cổng, do cho

phép kênh JFET mở trở lại. Dù sao ở trường hợp lý tưởng thì đây là cách nó hoạt động,

nhưng thực tế thì nó khơng hoạt động chút nào:

-

Tại sao lại như vậy? Tại sao kênh của JFET không mở trở lại và cho phép

dòng điện chạy qua như trước đây khi khơng có điện áp đặt giữa cổng và nguồn?

Câu trả lời nằm ở hoạt động của chuyển tiếp phân cực ngược cổng - nguồn. Miền

nghèo bên trong đường giao nhau đó hoạt động như một rào cản cách điện ngăn

cách cổng với nguồn. Như vậy, nó có một lượng điện dung nhất định có khả năng

lưu trữ điện tích. Sau khi được phân cực ngược một lượng điện tích được lưu trữ

ngay cả khi nguồn điện của điện áp đó bị ngắt. Điều cần thiết để bật lại JFET là xả

điện tích được lưu giữ giữa cổng và nguồn thơng qua một điện trở.

c. Điện trở xả:

15

-

Giá trị điện trở này không quan trọng. Điện dung của chuyển tiếp cổng -

nguồn này rất nhỏ và do đó ngay cả một điện trở xả có giá trị khá cao cũng tạo ra

một hằng số thời gian RC nhanh cho phép JFET tiếp tục dẫn với độ trễ nhỏ khi

công tắc được mở.

-

Đây cũng là mạch JFET công tắc hồn chỉnh để điều khiển bật/tắt một bóng

đèn.

C.

MẠCH PROTEUS

IV. SO SÁNH JFET VÀ MOSFET

A.

SO SÁNH JFET VÀ MOSFET

Loại

Tiêu chí

Đặc điểm

Chế độ hoạt

16

động

Trở kháng đầu

vào

Rò rỉ dòng điện

Chi phí sản xuất

Ứng dụng

Thích hợp cho các ứng dụng có

Thích hợp cho các ứng dụng độ

độ nhiễu thấp.

nhiễu cao.

GIỐNG: + Đều là Transistor điều khiển điện áp được sử dụng để khuếch đại tín hiệu.

+ Đều là các thiết bị đơn cực

B.

ƯU VÀ NHƯỢC ĐIỂM

Ưu điểm: Nhiệt độ ổn định, Trở kháng đầu vào cao vì vậy dịng điện đầu vào nhỏ vì

vậy cải thiện hiệu quả, năng lượng cao, có kích thước nhỏ.

Nhược điểm: Phản hồi chậm, hiệu suất thấp khi ở tần số cao.

17

TÀI LIỆU THAM KHẢO

[1] Microelectronic Circuits, Sedra & Smith, Chapter 5.

[2] Microelectronic Circuits 5th Solutions Manual, Sedra & Smith.

[3] Art of Electronics Student Manual, Hayes & Horowitz, Chapter 3.

[4] Transistor trường FET, Nguyễn Hoàng Hiệp.

[5] Các nguồn tài liệu tham khảo khác:

/> /> /> /> />

18