Giáo trình phân tích quy trình ứng dụng Mosfet với tín hiệu xoay chiều p4 doc

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (298.01 KB, 5 trang )

Giáo trình Linh Kiện Điện Tử

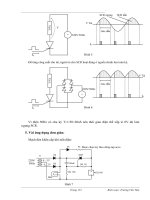

* Mạch tương đương của FET với tín hiệu nhỏ:

Người ta có thể coi FET như một tứ cự có dòng điện và điện thế ngõ vào là v

gs

và

i

g

. Dòng điện và điện thế ngõ ra là v

ds

và i

d

c

i

g

v

gs

v

ds

i

d

Hình 39

Do dòng

ig

rất nhỏ nên FET có tổng trở ngõ vào là:

g

gs

i

r =

π

rất lớn

v

Dòng thoát i

d

là một hà Với tín hiệ

ến thiên quanh điểm đi

m số theo v

gs

và v

ds

. u nhỏ (dòng điện và điện thế

chỉ bi ều hành), ta sẽ có:

Q

DS

DS

D

Q

gs

GS

D

D

v

v

i

v

v

i

i

∂

∂

+

∂

∂

=

Người ta đặt:

i

g

D

∂

=

và

i

1

D

∂

=

v

Q

GS

m

∂

vr

Q

DSo

∂

Ta có:

)gv

ods

=+=

oo

gsmd

r

1

ñaët theå (coù

r

1

vgi

v

gs

= r

π

.i

g

Các phương trình này được diễn tả bằng giản đồ sau đây gọi là mạch tương đương

xoay

Riêng đối

g mạch tương đương

người ta có thể b

chiều của FET.

với E-MOSFET, do tổng trở vào r

π

rất lớn, nên tron

ỏ r

π

v

gs

D

S

r

π

g

m

v

gs

r

0

v

ds

i

d

Hình 40

G

Trang 116 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

G D

i

d

v

gs

v

g

m

v

gs

r

0

ds

S

IX. IỆN DẪN TRUYỀN (TRANSCONDUCTANCE) CỦA

JFET VÀ DEMOSFET.

ũng tương tự như ở BJT, một cách tổng quát người ta định nghĩa điện dẫn truyền

của FET là tỉ số:

Đ

C

)t(v

)t(i

g

gs

d

m

=

của tiếp

tuyến v

Điện dẫn truyền có thể được suy ra từ đặc tuyến truyền, đó chính là độ dốc

ới đặc tuyến truyền tại điểm điều hành Q

Hình 41

Q

V

GS

(volt)

I

D

(mA)

Độ dốc tại điểm I

D

= I

DSS

là g

mo

∆V

GS

∆

I

D

V

GS(off)

I

DSS

Độ dốc tại điểm Q là:

)t(gs

)t(d

GS

D

GS

D

m

v

i

∆

V

I

V

dI

g =

∆

=

Về mặt toán học, từ phương trình truyền:

2

)off(GS

GS

DSSD

V

V

1II

⎥

⎥

⎦

⎤

⎢

⎢

⎣

⎡

−=

2

GS

DSS

V

V

1I

⎥

⎤

⎢

⎢

⎣

⎡

−=

)off(GS

D

I

⎥

⎦

Hình 42

d

=

Trang 117 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Ta suy ra:

2

GS

DSS

D

m

V

V

1I

dV

dI

g

⎥

⎥

⎤

⎢

⎢

⎡

−==

)off(GSGS

⎦⎣

⎥

⎥

⎤

⎦

⎢

⎢

⎣

⎡

−=−=

)off(GS

GS

)off(GS

DSS

m

V

V

1

V

I2

g

rị số của g

m

khi V

GS

= 0volt (tức khi I

D

=I

DSS

) được gọi là g

mo

.

ậy:

T

)off(GS

DSS

mo

V

I2

g

V

−=

ừ đó ta thấy:

⎥

⎥

⎦

⎤

⎢

⎢

⎣

⎡

−=

)off(GS

GS

mom

V

V

1gg

T

rong đó: g

m

n truyền của JFET hay DE-MOSFET vớ ỏ

g

mo

: là g

m

khi V

GS

= 0V

V

GS

: Điện thế phân cực cổng - nguồn

V

GS(off)

: Điện thế phân cực cổng - nguồn làm JFET hay DE-MOSFET ngưng.

ừ công thức:

: là điện dẫ i tín hiệu nh

T

2

)off(GS

GS

DSSD

V

V

1II

⎥

⎥

⎦

⎤

⎢

⎢

⎣

⎡

−=

⎥

⎥

⎦

⎤

⎢

⎢

⎣

⎡

−=

1

Ta suy ra:

Ngoài ra t

)off(GS

GS

DSS

D

V

V

I

I

ậy:

DSS

D

mom

I

I

gg =

V

Phương trình trên cho ta thấy sự liên hệ giữa điện dẫn truyền g

m

v

I

ới dòng điện thoát

V

GS(off)

do nhà sản

xuất cung c

ông thức tính dòng điện thoát I

D

theo V

GS

của E-MOSFET khác với JFET và

DE-MOSFET nên điện dẫn truyền của nó cũng khác.

ừ công thức truyền của E-MOSFET

Ta có:

D

tại điểm điều hành Q. g

mo

được xác định từ các thông số I

DSS

và

ấp.

X. ĐIỆN DẪN TRUYỀN CỦA E-MOSFET.

Do c

T

[]

2

)th(GSGSD

VVKI −=

[]

[

]

2

)th(GSGS

GSGS

D

m

VVK

dV

d

dV

dI

g −==

[

]

)th(GSGSm

VVK2g −=

)th(GS

D

GS

V

K

I

V += Ngoài ra:

Dm

KI2g =

Thay vào trên ta được:

Trong đó:

g

m

: là điện dẫn truyền của E-MOSFET cho tín hiệu n

K: là hằng số với đơn vị Amp/volt

2

c thoát D

hỏ

I

D

: Dòng diện phân cực cự

Trang 118 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Ta thấy g

m

tùy thuộc vào dòng điện thoát I

D

, nếu gọi g

m1

là điện dẫn truyền của E-

MOSFET ứng với dòng thoát I

D1

và g

m2

là điện dẫn truyền của E-MOSFET ứng với dòng

thoát I

D2

Ta có:

1D1m

KI2g =

và

2D2m

KI2g =

nên:

1D

2D

1m2m

I

I

gg =

−

I

D

(mA)

I

D1

Q

I

Dmax

[

]

2

)

th

(

GSGSD

VVKI −=

dốc tại Q là g

m1

Độ

V

GS(th)

0

V

GS

(volt)

XI. TỔNG TRỞ VÀO VÀ TỔNG TRỞ RA CỦA FET.

Hình 43

- Giống như ở BJT, người ta cũng dùng hiệu ứng Early để định nghĩa tổng trở ra của

FET (ở vùng bảo hòa, khi V

DS

tăng, dòng điện I

D

cũng hơi tăng và chùm đặc tuyến ra

cũng hội tụ tại một điểm gọi là điện thế Early).

Nếu gọi V

A

là điện thế Early ta có:

FET cuûa ratrôû Toång : r

o

D

A

o

I

V

r =

−

r

o

như vậy thAy đổi theo dòng thoát I

D

và có trị số khoảng vài MΩ đến hơn

10MΩ

- Do JFET thường được dùng theo kiểu hiếm (phân cực nghịch nối cổng - nguồn)

nên t ng trở vào lớn (hàng trăm MΩ). Riêng E-MOSFET và DE-MOSFET do cực cổng

cách điện hẳn khỏi cực nguồn nên tổng trở vào rất lớn (hàng trăm MΩ). Kết quả là người

ta có thể xem gần đúng tổng trở vào của FET là vô hạn.

Với FET : r

π

≈ ∞ Ω

0

V

DS

(volt)

Early voltage

I

D

(m A) V

GS

Hình 44

ổ

Trang 119 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Trong các mạch sử dụng với tín hiệu nhỏ người ta có thể dùng mạch tương đương

cho FET như hình (a) hoặc hình (b). Nếu tải không lớn lắm, trong mạch tương đương

ình 45

XII. CMOS TUYẾN TÍNH (LINEAR CMOS).

một E-MOSFET kênh N mắc như hình sau

đây t

hật ra nó được cấu trúc như sau:

i ta có thể bỏ cả r

o

ngườ

H

Nếu ta có một E-MOSFET kênh P và

a được một linh kiện tổ hợp và được gọi là CMOS (Complementary MOSFET).

T

v

G

S

r

π

g

m

v

gs

r

0

v

ds

i

Hình 45 (a)

gs

D

d

v

gs

D

S

g

m

v

gs

r

0

v

ds

i

d

Hình 45 (b)

v

gs

G

D

S

g

m

v

gs

v

ds

i

d

Hình 45 (c)

G

G

1

S

1

D

1

G

2

2

S

2

D

v

i

(t) v

0

(t)

kênh P

Q

Q

1

E-MOSFET

Q

2

E-MOSFET

kênh N

1

Q

2

Hình 46

Trang 120 Biên soạn: Trương Văn Tám

.