Giáo trình phân tích quy trình ứng dụng Mosfet với tín hiệu xoay chiều p1 pdf

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (323 KB, 5 trang )

Giáo trình Linh Kiện Điện Tử

V63,0V

PS

−=V

G

iện thế nghẽn ở nhiệt độ bình thường.

Các đây mô tả ảnh hưởng a nhiệ trên các đặc tuyến ra, đặc tuyến

truyền và đặc tuyến của dòng I

D

theo nhiệt đ h V làm thông số.

c hạt tải điện

trong

leaka

GSS GSS

phân c nghịch nối P-N giữa cực cổng và cực nguồn. Dòng điện này là dòng điện rỉ

cổng-nguồn khi nối tắt cực nguồn với cực thoát. Dòng I

GSS

tăng gấp đôi khi nhiệt độ tăng

lên 10

0

C.

với V

P

là đ

hình vẽ sau củ t độ

ộ k i

GS

I

D

0

V

GS

= 0

V

GS

= -1V

|V

GS

| = |V

P

|-0,63V

I

D

giảm

V

DS

25

0

45

0

I

D

tăng

Hình 18

0

-100 -50 0 50 100

150

I

D

I

D

I

(V

DS

cố định)

-55

0

C 25

0

C +150

0

C

Ngoài ra, một tác dụng thứ ba của nhiệt độ lên JFET là làm phát sinh cá

vùng hiếm giữa thông lộ-cổng và tạo ra một dòng điện rỉ cực cổng I

GSS

(gate

ge current). Dòng I

được nhà sản xuất cho biết. dòng rỉ I chính là dòng điện

cự

DSS

|V

GS

| = |V

P

|-0,63V

V

GS(of

f

V

GS

t

0

C

|V

GS

| = |V

P

|-0,63V

V

GS

= -1V

V

GS

= -0V

Hình 19

Trang 101 Biên soạn: Trương Văn Tám

Giáo trình phân tích quy trình ứng dụng

Mosfet với tín hiệu xoay chiều

Giáo trình Linh Kiện Điện Tử

10

)25(

00

2)25()(

−

=

t

GSSGSS

CICtI

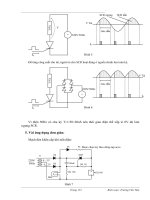

V. MOSFET LOẠI HIẾM (DEPLETION MOSFET: DE

MOSFET)

Ta thấy rằng khi áp một điện thế âm vào J nh N thì vùng hiếm rộng ra. Sự gia

tăng của vùng hiếm làm cho thông lộ hẹp lại và điện trở của thông lộ tăng lên. Kết quả

sau cùng là tạo ra dòng điện I

D

nhỏ hơn I

DSS

.

Bây giờ, nếu ta áp điện thế dương V

GS

vào JFET kênh N thì vùng hiếm s ẹp lại

(do phân cực thuận cổng nguồn), thông lộ rộng ra và điện trở thông lộ giảm xuống, kết

quả là dòng điện

ớn hơ .

Trong các ứng dụng thông thường, người ta đều phân cực n ch nối cổng nguồ

(V

GS

âm đối với JFET kênh N và dương đối với JFET kênh P) và được gọi là điều hành

theo kiểu hiếm.

JFET cũng có thể điều eo kiể ng (V

GS

dươn i JFET kênh N và âm

đối với JFET kênh P) nhưng ít khi được ứng dụng, vì mục đích của JFET là tổng trở vào

lớn, nghĩa là dòng điện I

G

ở cực cổng - nguồn trong JFET sẽ làm giảm tổng trở vào, do

đó thông thường người ta giới hạn trị số phân cực thuận của nối cổng - nguồn tố

0,2V (trị số danh định là 0,5

V

GG

G

D

S

I

GSS

V

DS

= 0

Hình 20

V

V).

i đa là

g đối vớ

u tă hành th

n ghị

n I

DSS

I

D

sẽ l

ẽ h

FET kê

Trang 102 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Tuy JFET có tổng trở vào khá lớ ũng còn khá nhỏ so với đèn chân không.

Để tăng tổng trở vào, người ta đã tạo ại transistor trường khác sao cho cực cổng

cách iện hẳn cực nguồn. Lớp cách điện là Oxyt bán dẫn SiO

2

nên transistor được gọi là

MOS ET.

a phân biệt hai loại MOSFET: MOSFET loại hiếm và MOSFET loại tăng.

ình sau đây mô tả cấu tạo căn bản MOSFET loại hiếm (DE - MOSFET) kênh N và kênh

.

n nhưng c

một lo

đ

F

T

H

P

V

GG

G

D

I

S

GSS

V

DS

V

DD

+

-

V

GS

+

Phân cực ki

ể

u

hiếm

Phân cực ki

ể

u

tăng

(Tối đa 0,2V)

-

+

-

+

-

0 0 -4V

V

GS

V

GS

= 0,2V

V

GS

= 0V

V

GS

= -1V

V

GS

= -2V

S

= -3V

V

DS

I

D

I

D

I

DSS

Điều hành

kiểu tăng

Điều hành

kiểu hiếm

0,2V

Hình 21

JFET kênh N

+

V

GG

G

D

S

V

DS

V

DD

V

GS

-

+

Phân cực ki

-

ể

u

hiếm

Phân cực ki

ể

u

tăng

(Tối đa 0,2V)

-

+

-

+

V

GG

I

D

Hình 22

V

G

Trang 103 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Thân p-

Kênh n-

n+

n+

Nguồn

S

Cổng

G

Thoát

D

Tiếp xúc

kim loại

SiO

2

G

D

S

Thân U

G

D

S

Thân nối với

nguồn

Ký

DE-MOSFET kênh N

Hình 23

hiệu

Thân n-

Kênh p-

p+ p+

Nguồn

S

Cổng

G

Thoát

D

Tiếp xúc

kim loại

SiO

2

G

D

Thâ

S

n U

G

Thân nối với

nguồn

Hình 24

Ký hiệu

D

S

DE-MOSFET kênh P

Trang 104 Biên soạn: Trương Văn Tám

.

Giáo trình Linh Kiện Điện Tử

Chú ý rằng DE - MOS thoát D, cực nguồn S, cực cổng G và thân

U (subtrate). Trong các ứng dụng thông thường, thân U được nối với nguồn S.

Đ SFET hoạt động, người ta áp điện V

DD

vào cực thoát và cực

nguồn ( ng của ngu iện nối với cực thoát D và cực âm nối với cực nguồn S

trong DE-MOSFET kênh N và ngược lại trong DE-MOSFET kênh P). Điện thế V

GS

giữa

cực cổ nguồn có thể âm (DE-MOSFET kênh N điều hành theo kiểu hiếm) hoặc

dương SFET kênh iều hành theo kiểu tăng)

FET có 4 cực: cực

ể DE-MO

cực dươ

một nguồn

ồn đ

ng và cực

(DE-MO N đ

S

Thân p-

n+

Kênh n-

G

D

SiO

2

- V

DD

+

+ V

GG

-

n+

Thân p-

Kênh n-

n+

thoát

Vùng hiếm do cổng âm đẩy các điện tử

và thoát dương hút các điện tử về nó

Tiếp xúc kim

loại cực cổng

Vùng hiếm giữa

phân cực nghịch p-

và vùng thoát n+

Điều

hành

theo

kiểu

hiếm

Hình 25

Trang 105 Biên soạn: Trương Văn Tám

.