Transistor hiệu ứng trường FET Phần 1.pdf

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (666.97 KB, 13 trang )

Chương 6

1

CHƯƠNG 6: TRANSISTOR HIỆU ỨNG TRƯỜNG FET

6.1 Giới thiệu

6.2 Lý thuyết hoạt động của JFET

6.3 Lý thuyết hoạt động của MOSFET

6.4 Giải tích đồ thò và phân cực

6.5 Giải tích tín hiệu lớn – Sự sái dạng

6.6 Giải tích tín hiệu nhỏ

6.7 Mở rộng

Chương 6

2

6.1 Giới thiệu

Transistor hiệu ứng trường (Field Effect Transistor – FET):

9 JFET: Junction FET

9 MOSFET: Metal-Oxid Semiconductor FET (Insulated-Gate – IGFET)

Tính chất (Phân biệt với BJT)

9 Nhạy với điện áp (voltage-sensitive)

9 Trở kháng vào rất cao

6.2 Lý thuyết hoạt động của JFET

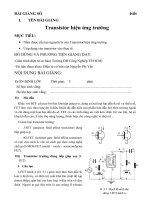

6.2.1 Cấu tạo (n-channel JFET):

Chương 6

3

6.2.2 Hoạt động:

Giả sử S và G nối đất; v

DS

> 0:

⇒ Dòng i

D

: D → S: Phụ thuộc vào v

DS

và Điện trở kênh n (R

n-Channel

)

Dòng i

Channel – Gate

≈ 0: Do Diode tạo bởi tiếp xúc pn Channel-Gate phân cực nghòch

(a) Khi v

DS

tăng: Vùng khuyết (depletion region – vùng gạch chéo) tăng → R

n-Channel

tăng

(b) v

DS

= V

po

(Điện áp nghẽn: pinch-off voltage): Hai vùng khuyết chạm nhau: i

D

= I

po

Chương 6

4

(c) v

DS

> V

po

: V

a

= V

po

= const → i

D

= I

po

= const

(d) v

DS

= BV

DSS

: Điện áp đánh thủng.

Đồ thò:

Giả sử v

DS

= const; v

GS

thay đổi:

v

GS

< 0: Tăng vùng khuyết → i) R

Channel

tăng → i

D

giảm

ii) V

po

giảm

v

GS

> 0: Giảm vùng khuyết → i) R

Channel

giảm → i

D

tăng

ii) V

po

tăng

Chương 6

5

⇒ “Voltage-Sensitive Device”

Đồ thò:

Lưu ý: n-JFET: Phân cực sao cho không có dòng I

Channel-Gate

(v

GS

≤ 0 hoặc v

GS

nhỏ > 0)

6.2.3 Đặc tuyến:

Điện áp v

DS

tại điểm nghẽn: v

DS-Pinch Off

= V

p

= V

po

+ v

GS

Điện áp đánh thủng: BV

DSX

≈ BV

DSS

+ v

GS

Đặc tuyến VA trong vùng bão hòa (Giữa điện áp nghẽn và đánh thủng: V

p

< v

DS

< BV

DSX

)

i

D

=

⎥

⎥

⎦

⎤

⎢

⎢

⎣

⎡

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

−++

2/3

2

3

1

po

GS

po

GS

po

V

v

V

v

I

với v

GS

< 0

Nhận xét: v

GS

= 0: i

D

= I

po