bài tập kĩ thuật số bk đà nẵng

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (608.04 KB, 5 trang )

Bài tập Kỹ Thuật Số (HVT 2017) – Dành cho SV ngành Điện Tử - Viễn Thông – Học kỳ 1, 2017-2018

BÀI TẬP KỸ THUẬT SỐ

This assignment is to be done individually. You may talk to classmates/TAs/instructors about general problemsolving approaches, but do not discuss specific solutions.

1. Chứng minh các đẳng thức sau bằng đại số

a. AB AD BCD ( A D)( A C )( B D)

b.

CD BC ABD ( A C )( B C )( B D)

c.

Z XY X Z ( X Z )(Y Z )

2. Cho bảng chân trị sau

C B A F1 F2

0 0 0 0 1

0 0 1 0 0

0 1 0 1 0

0 1 1 0 1

1 0 0 0 1

1 0 1 1 1

1 1 0 0 1

1 1 1 1 0

a. Viết biểu thức hàm F1 dưới dạng tối thiểu hóa của tích các tổng (Product-of-Sums / POS)?

b. Viết biểu thức hàm F2 dưới dạng tối thiểu hóa của tổng các tích (Sum-of-Products / SOP)?

3. Dùng bìa Karnaugh rút gọn các hàm sau

a. F1 ( A, B, C, D) (1,2,4,7,9,15) d (3,5)

b. F2 ( A, B, C, D) (0,1,2,4,5,8,10,11,14,15)

c. F3 ( A, B, C, D) (2,5,7,8,13,15) d (0,10)

d. F4 ( A, B, C, D) (0,2,4,5,6,8,10,12,13)

e. F5 (A, B, C, D) = (0, 1, 2, 4, 6, 7, 8, 9, 13, 15)

f. F6 (A, B, C, D) = (0, 1, 5, 8, 12, 14, 15) + d(2, 7, 11)

g. F7 (A, B, C, D) = (1, 2, 4, 9, 11)

h. F8 (A, B, C, D) = (0, 1, 4, 5, 10, 11, 12) + d(3, 8, 14)

i. F9 (A, B, C, D) = (0, 2, 3, 4, 7, 8, 14)

j. F10 (A, B, C, D) = (1, 2, 4, 15) + d(0, 3, 14)

4. Rút gọn hàm sau và thực hiện bằng cổng NAND 2 ngõ vào

F ( A, B, C, D) (4,6,9,10,12,14) d (8,11,13)

5. Rút gọn hàm sau và thực hiện bằng cổng NOR 2 ngõ vào

F ( A, B, C, D) (0,2,3,4,6,9,10,11) d (7,13,15)

6. Thực hiện hàm F ( A, B, C, D) B(C D) ACD chỉ dùng cổng NAND

7. Thực hiện hàm F ( A, B, C, D) ( A B)(C BCD) chỉ dùng cổng NOR

- 1/5 -

Bài tập Kỹ Thuật Số (HVT 2017) – Dành cho SV ngành Điện Tử - Viễn Thông – Học kỳ 1, 2017-2018

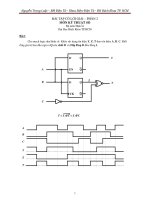

8. Cho mạch như hình vẽ.

a) Viết bảng chân trị (True Table) của hàm f?

b) Nếu mỗi cổng trong mạch trên được chế tạo theo công nghệ CMOS, cần bao nhiêu transistors để

thực hiện được mạch?

9. Cho các mạch logic trên hình vẽ

a) Viết bảng chân trị của các hàm f?

b) Tìm phương trình rút gọn ở dạng chính tắc 1 (SOP) của các hàm trên?

a)

b)

10. Tối thiểu hóa và vẽ sơ đồ thực hiện các hàm sau đây theo công nghệ CMOS.

a) f(x, y, z) = (0, 4, 5) + d(6, 7)

b) g(x, y, z) = (2, 3, 4) + d(0, 1)

c) h(x, y, z, w) = (0, 1, 2, 4, 5, 6, 8, 9, 10)

d) y(a, b, c, d) = (0, 1, 2, 4, 6, 8, 10, 12, 14)

11. Download and install the ModelSim PE Student Edition on your computer at

/>Before downloading, carefully read through the installation instruction on the website. Note that you need to

have an email account and internet access in order to register and activate the software. Once finished,

print your desktop which shows proof of your installation as shown in the example below:

- 2/5 -

Bài tập Kỹ Thuật Số (HVT 2017) – Dành cho SV ngành Điện Tử - Viễn Thông – Học kỳ 1, 2017-2018

12. Trình bày những khác biệt cơ bản giữa cổng logic và Flip-Flop.

13. So sánh mạch số tổ hợp và mạch số tuần tự.

14. Thiết kế mạch mã hóa nhị phân ưu tiên từ 4 sang 2; biết các ngõ vào tích cực mức thấp và ngõ vào x0 có

mức ưu tiên cao nhất.

(Yêu cầu: vẽ sơ đồ khối, trình bày bảng trạng thái, phương trình logic các ngõ ra theo các ngõ vào, sơ đồ

mạch thực hiện)

15. Thiết kế mạch mã hóa nhị phân ưu tiên từ 8 sang 3; biết các ngõ vào tích cực mức thấp và ngõ vào x7 có

mức ưu tiên cao nhất.

16. Chuyển sơ đồ mạch ở bài 14 về sử dụng một loại cổng (NAND hoặc NOR).

17. Chuyển sơ đồ mạch ở bài 15 về sử dụng một loại cổng (NAND hoặc NOR).

18. Thiết kế mạch giải mã nhị phân từ 3 sang 8, với các ngõ ra tích cực mức thấp (mức 0).

19. Chuyển sơ đồ mạch ở bài 18 về sử dụng một loại cổng (NAND hoặc NOR).

20. Thiết kế mạch cộng toàn phần 2 số nhị phân 1-bit (Full-Adder)

21. Thiết kế mạch trừ toàn phần 2 số nhị phân 1-bit (Full-Subtractor).

- 3/5 -

Bài tập Kỹ Thuật Số (HVT 2017) – Dành cho SV ngành Điện Tử - Viễn Thông – Học kỳ 1, 2017-2018

22**. Thiết kế mạch cộng trừ toàn phần 2 số nhị phân 1-bit (Full Adder-Subtractor) cho phép cộng hoặc trừ

2 số nhị phân 1 bit. (Gợi ý: thêm tín hiệu S cho phép lựa chọn thực hiện phép toán cộng hay trừ: S=0: cộng,

S=1: trừ).

23**. Thiết kế mạch logic nhân 5 NHỎ NHẤT với ngõ vào 4 bits và ngõ ra 8 bits như bảng sự thật dưới đây.

Các bài tập sử dụng ngôn ngữ mô tả phần cứng Verilog HDL

24. Mô tả mạch cộng bán phần 1-bit HA bằng Verilog.

25. Mô tả mạch cộng toàn phần 1-bit FA (đã thiết kế ở bài 20) bằng Verilog bằng cách sử dụng lại module

HA đã mô tả ở bài tập trước. Viết testbed (testbench) để kiểm tra module FA. Trình bày các kết quả đã thực

hiện trong phần mềm ModelSIM.

26. Mô tả mạch trừ toàn phần 1-bit FS đã thiết kế ở bài 21 bằng Verilog. Viết testbed (testbench) để kiểm tra

và trình bày các kết quả đã thực hiện trong phần mềm ModelSIM.

27. Mô tả module mạch giải mã LED 7-đoạn loại anode chung bằng Verilog.

28. Mô tả mạch giải mã nhị phân từ 2 sang 4 với các ngõ ra tích cực mức cao bằng Verilog. Viết testbed

(testbench) để kiểm tra và trình bày các kết quả đã thực hiện trong phần mềm ModelSIM.

29. Mô tả mạch giải mã nhị phân từ 3 sang 8 đã thiết kế ở bài 18 bằng Verilog. Viết testbed (testbench) để

kiểm tra và trình bày các kết quả đã thực hiện trong phần mềm ModelSIM.

30**. Mô tả mạch cộng-trừ toàn phần 1-bit đã thiết kế ở bài 22 bằng Verilog. Viết testbed (testbench) để

kiểm tra và trình bày các kết quả đã thực hiện trong phần mềm ModelSIM.

31**. Thực hiện thiết kế ở bài 23 bằng Verilog. Viết testbed (testbench) để kiểm tra và trình bày các kết quả

đã thực hiện trong phần mềm ModelSIM.

32. Thực hiện mạch cho ở hình bên dưới bằng Verilog. Viết testbed (testbench) để kiểm tra và trình bày các

kết quả đã thực hiện trong phần mềm ModelSIM.

MUX 2-1

A

B

C

I0

Decoder 2-4

O0

I0

O1

O

I1

I1

S

- 4/5 -

O2

O3

F

Bài tập Kỹ Thuật Số (HVT 2017) – Dành cho SV ngành Điện Tử - Viễn Thông – Học kỳ 1, 2017-2018

33. Thiết kế bộ đếm nối tiếp (đếm không đồng bộ), đếm xuống, đếm 8 (trạng thái), sử dụng JKFF có xung

clock CK tích cực sườn xuống.

34. Thiết kế bộ đếm nối tiếp, đếm lên, đếm 6, sử dụng TFF có xung clock CK tích cực sườn lên và tín hiệu

xung xóa CLR tích cực mức thấp.

35. Thiết kế bộ đếm song song (đếm đồng bộ), đếm lên, đếm 6, sử dụng TFF có xung clock CK tích cực

sườn lên và tín hiệu xung xóa CLR tích cực mức thấp.

36. Thiết kế bộ đếm song song, đếm lên, đếm 6, sử dụng SRFF có xung clock CK tích cực sườn lên và tín

hiệu xung xóa CLR tích cực mức thấp.

37. Thiết kế bộ đếm song song, đếm lên, đếm 10, sử dụng JKFF có xung clock CK tích cực sườn lên và tín

hiệu xung xóa CLR tích cực mức thấp.

38. Thiết kế bộ đếm song song, đếm xuống, đếm 7, sử dụng JKFF có xung clock CK tích cực sườn xuống và

tín hiệu xung xóa CLR tích cực mức thấp.

39. Thiết kế bộ đếm song song, đếm thuận nghịch, đếm 5, sử dụng DFF có xung clock CK tích cực sườn

xuống và tín hiệu xung xóa CLR tích cực mức thấp.

40. Thiết kế bộ đếm nối tiếp, đếm thuận nghịch, đếm 16 (Kđ=16), dùng JKFF có xung Ck kích khởi theo

sườn lên, với X là tín hiệu điều khiển chiều đếm được qui ước như sau: X=0: mạch đếm lên, X=1: mạch đếm

xuống.

41. Thiết kế bộ đếm song song (đếm đồng bộ), đếm lên, đếm 5 (Kđ=5), theo mã Gray, dùng JKFF.

42. Thiết kế bộ đếm hỗn hợp, đếm 20, đếm lên dùng JKFF có xung Ck tích cực sườn lên.

43*. Một hệ thống điều khiển đóng mở cửa tự động của bãi đỗ xe ô tô tự động chấp nhận các tờ tiền giấy

loại 5.000đ và 10.000đ. Cửa sẽ mở cho ô tô vào bãi đỗ khi tổng số tiền nạp vào là 15.000đ, và tiền thừa (nếu

có) sẽ được trả lại. Khi cửa đã mở cho xe đi vào, hệ thống sẽ tự động quay trở về trạng thái ban đầu.. Yêu

cầu:

a. Thiết kế khối điều khiển cho hệ thống đóng mở cửa tự động nói trên sử dụng máy trạng thái loại

Moore và DFF. Mô phỏng khối mạch điều khiển bằng phần mềm CircuitMaker (hoặc phần mềm tương

tự thích hợp) và trình bày kết quả mô phỏng.

b. Mô tả khối điều khiển ở câu a) bằng ngôn ngữ Verilog, mô phỏng hệ thống sử dụng ModelSIM và

trình bày kết quả dạng sóng mô phỏng.

44. Một bộ đếm thực hiện chức năng đếm các giá trị lần lượt theo thứ tự là 1, 3, 5,7, 1, 3, 5 ... Khi tín hiệu

CE (Count Enable) =1, bộ đếm sẽ đếm và ngừng đếm khi CE=0. Khi nhấn Reset không đồng bộ tích cực

mức thấp, bộ đếm sẽ được reset về giá trị đếm 1. Thiết kế bộ đếm nói trên sử dụng Flip flop JK.

45. Một mạch số với một đầu vào X, một đầu ra Z, xung Clk tích cực sườn lên, tín hiệu Reset bất đồng bộ

tích cực mức cao, mạch hoạt động như sau:

-Tín hiệu vào X là chuỗi 0 hoặc 1 xuất hiện ngẫu nhiên

-Z=1 nếu gặp dãy bit đầu vào là 101 hoặc 011

-Z=0 trong các trường hợp khác

a. Biểu diễn hoạt động của mạch trên bằng sơ đồ chuyển trạng thái loại Moore (hoặc Mealy)

b. Thiết kế (thực hiện) mạch sử dụng DFF (hoặc SRFF, hoặc JKFF).

c. Mô phỏng khối mạch điều khiển bằng phần mềm CircuitMaker (hoặc phần mềm tương tự thích hợp) và

trình bày kết quả mô phỏng.

d. Biểu diễn mạch bằng Verilog HDL, sau đó viết testbench thực hiện mô phỏng kiểm tra mạch trong

ModelSIM và trình bày dạng sóng mô phỏng.

-- Good luck -- 5/5 -