Bài giảng kỹ thuật số và vi xử lý chương 5 đh bách khoa

Bạn đang xem bản rút gọn của tài liệu. Xem và tải ngay bản đầy đủ của tài liệu tại đây (153.37 KB, 23 trang )

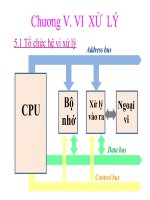

Chương V. VI XỬ LÝ

5.1 Tổ chức hệ vi xử lý

CPU

Bộ

nhớ

Address bus

Xử lý

vào ra

Ngoại

vi

Data bus

Control bus

INT0*

INT1*

Timer 0 Timer 1

Serial port

Interrupt

control

Registers

128 Byte

RAM

ROM

Timer 1

Timer 0

CPU

Oscillator

Bus

control

EA

RST

I / O ports

Serial

port

ALE

PSEN

TXD* RXD*

T1*

T0*

Bộ nhớ trên chip

27

26

25

24

23

22

21

20

1F

18

17

10

0F

08

07

3F

37

2F

27

1F

17

0F

07

3E

36

2E

26

1E

16

0E

06

3D 3C 3B

35 34 33

2D 2C 2B

25 24 23

1D 1C 1B

15 14 13

3

0DBank

0C 0B

05 04 03

Bank 2

Bank 1

Bank 0

3A

32

2A

22

1A

12

0A

02

39

31

29

21

19

11

09

01

38

30

28

20

18

10

08

00

Bộ nhớ trên chip

7F

RAM đa dụng

30

2F 7F 7E 7D 7C

2E 77 76 75 74

2D 6F 6E 6D 6C

2C 67 66 65 64

2B 5F 5E 5D 5C

2A 57 56 55 54

29 4F 4E 4D 4C

7B

73

6B

63

5B

53

4B

7A

72

6A

62

5A

52

4A

79

71

69

61

59

51

49

78

70

68

60

58

50

48

A0

A7 Bộ

A6 nhớ

A5 A4trên

A3 chip

A2 A1 A0

99

Không được địa chỉ hóa bit SBUF

98

9F 9E 9D 9C 9B 9A 99 98 SCON

90

97 96 95 94 93 92 91 90

89

Không được địa chỉ hóa bit

8D

88

8F 8E 8D 8C 8B 8A 89 88 TCON

Không được địa chỉ hóa bit PCON

87

83

81

Không được địa chỉ hóa bit

P1

P1

Bộ nhớ trên chip

FF

F0

F7 F6 F5 F4 F3 F2 F1 F0

B

E0

E7 E6 E5 E4 E3 E2 E1 E0

ACC

D0

D7 D6 D5 D4 D3 D2 -- D0 PSW

B8

--

B0

B7 B6 B5 B4 B3 B2 B1 B0

P3

A8

AF --

IE

--

-- BC BB BA B9 B8

-- AC AB AA A9 A8

IP

5.3 Tập lệnh

Các lệnh xử lý số học :

ADD A,Rn

(1,1)

SUBB A,data

SUBB A,@Ri

SUBB A,#data

INC A

INC Rn

INC data

INC @Ri

DEC A

DEC Rn

(2,1)

(1,1)

(2,1)

(1,1)

(1,1)

(2,1)

(1,1)

(1,1)

(1,1)

Các lệnh luận lý:

ANL

ANL

ANL

ANL

ANL

ANL

ANL

ANL

ORL

ORL

ORL

A,Rn

A,data

A,@Ri

A,#data

data,A

data,#data

C,bit

C,bit

A,Rn

A,data

A,@Ri

(1,1)

(2,1)

(1,1)

(2,1)

(2,1)

(3,2)

(2,2)

(2,2)

(1,1)

(2,1)

(1,1)

ORL

ORL

ORL

ORL

XRL

XRL

XRL

XRL

data,A

data,#data

C,bit

C,bit

A,Rn

A,data

A,@Ri

A,#data

(2,1)

(3,2)

(2,2)

(2,2)

(1,1)

(2,1)

(1,1)

(2,1)

CPL A

CPL C

CPL bit

RL A

RLC A

RR A

RRC A

SWAP A

(1,1)

(1,1)

(2,1)

(1,1)

(1,1)

(1,1)

(1,1)

(1,1)

Các lệnh chuyển dữ liệu :

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

A,Rn

A,data

A,@Ri

A,#data

Rn,A

Rn,data

Rn,#data

data,A

(1,1)

(2,1)

(1,1)

(2,1)

(1,1)

(2,2)

(2,1)

(2,1)

MOV @Ri,data

MOV @Ri,#data

MOV DPTR,#data16

MOV C,bit

MOV bit,C

MOV A,@A+DPTR

MOV A,@A+PC

MOVX A,@Ri

MOVX A,@DPTR

MOVX @Ri,A

MOVX @DPTR,A

PUSH data

POP data

(2,2)

(2,1)

(1,1)

(2,1)

(2,2)

(1,1)

(1,2)

(1,2)

(1,2)

(1,2)

(1,2)

(2,2)

(2,2)

Các lệnh chuyển điều khiển :

ACALL

addr11

LCALL

addr16

RET

RETI

AJMP

addr11

LJMP

addr16

SJMP

rel

JMP

@A+DPTR

JZ

rel

JNZ

rel

JC

rel

JNC

rel

JB

bit,rel

(2,2)

(3,2)

(1,2)

(1,2)

(2,2)

(3,2)

(2,2)

(1,2)

(2,2)

(2,2)

(2,2)

(2,2)

(3,2)

JNB

bit,rel

(3,2)

JBC

bit,rel

(3,2)

CJNE

A,data,rel (3,2)

CJNE

A,#data,rel (3,2)

CJNE

Rn,#data,rel (3,2)

CJNE

A,data,rel (3,2)

CJNE @Ri,#data,rel (3,2)

DJNZ

Rn,rel

(2,2)

DJNZ

data,rel

(3,2)

CÁC CHẾ ĐỘ TIMER

- Chế độ 0 : timer 13 bit

Ck

TLX

THX

5 bit

8 bit

TFX

- Chế độ 1 : timer 16 bit

Ck

TLX

THX

TFX

- Chế độ 2 : tự động nạp lại 8 bit

TLX hoạt động như timer 8 bit còn THX lưu giá trị

được nạp. Khi số đếm tràn từ FFH đến 00H cờ timer

sẽ được set và giá trị trong THX sẽ được nạp vào

TLX .

- Chế độ 3 : timer 0 tách thành hai timer 8 bit, TL0 có

cờ tràn TF0 và TH0 có cờ tràn TF1 .

CÁC THANH GHI ĐIỀU KHIỂN TIMER

SFR

Mục đích

Địa chỉ

Địa chỉ bit

TCON

Điều khiển

88H

TMOD

Chế độ

89H

không

TL0

Byte thấp

timer 0

8AH

không

TL1

Byte thấp

timer 1

8BH

không

có

CÁC THANH GHI ĐIỀU KHIỂN TIMER

SFR

Mục đích

Địa chỉ

Địa chỉ bit

TH0

Byte cao

timer 0

8CH

không

TH1

Byte cao

timer 1

8DH

không

THANH GHI ĐIỀU KHIỂN TIMER (TCON)

Bit

Ký hiệu

Địa chỉ

Chức năng

TCON .7

TF1

8FH

Cờ tràn timer1

TCON.6

TR1

8EH

Bit ĐK timer1 chạy

TCON.5

TF0

8DH

Cờ tràn timer0

TCON.4

TR0

8CH

Bit ĐK timer0 chạy

THANH GHI ĐIỀU KHIỂN TIMER (TCON)

Bit

Ký hiệu

Địa chỉ

Chức năng

TCON .3

IE1

8BH

Cờ cạnh ngắt 1

TCON.2

IT1

8AH

Cờ kiểu ngắt 1

TCON.1

IE0

89H

Cờ cạnh ngắt 0

TCON.0

IT0

88H

Cờ kiểu ngắt 0

THANH GHI CHẾ ĐỘ TIMER (TMODE)

Bit

Ký hiệu Timer

Chức năng

7

GATE

1

Bit mở cổng

6

C/T

1

Bit chọn chế độ :

1 : đếm sự kiện

0 : định thời

5

M1

1

Bit 1 của chế độ

4

M0

1

Bit 0 của chế độ

00 : chế độ 0

01 : chế độ 1

10 : chế độ 2

THANH GHI CHẾ ĐỘ TIMER (TMODE)

Bit

Ký hiệu Timer

Chức năng

3

GATE

0

Bit mở cổng

2

C/T

0

Bit chọn chế độ :

1 : đếm sự kiện

0 : định thời

1

M1

0

Bit 1 của chế độ

0

M0

0

Bit 0 của chế độ